EP1C4F324C7N FPGA: Datový list, funkce, programování a specifikace

Tato příručka je o EP1C4F324C7N, typu čipu FPGA vyrobeného společností Intel.Je to skvělé pro projekty, které vyžadují silný výkon, ale také musí zůstat v rozpočtu.V tomto článku se dozvíte, co tento čip může udělat, jak to funguje, kde se používá a jak jej naprogramovat.Ať už pracujete na elektronice pro automobily, továrny nebo dokonce domácí zařízení, tato příručka vám pomůže pochopit, proč je EP1C4F324C7N inteligentní a flexibilní volba.Katalog

Přehled EP1C4F324C7N

The EP1C4F324C7N je součástí řady Intel's Cyclone® FPGA, speciálně navržená pro nákladově efektivní aplikace vyžadující dobrou rovnováhu výkonu a nízkých nákladů.Tato FPGA obsahuje 4 000 logických prvků a 400 bloků logických pole (LABS), což poskytuje robustní schopnosti pro mírné návrhy složitosti.Zahrnuje 76,5 kilobitů celkového RAM a podporuje až 249 I/O kolíků, což je velmi všestranné pro různé požadavky na propojení.EP1C4F324C7N je vybavena pro zpracování náročných aplikací, která pracuje na frekvencích až do 320 MHz as rozsahem napájecího napětí 1,425 V až 1,575 V, EP1C4F324C7N.Podporuje širokou škálu standardů I/O, jako jsou LVTTL, LVCMOS, SSTL-2 a SSTL-3, a je kompatibilní s externími typy paměti, jako je DDR SDRAM, což zvyšuje jeho užitečnost při zpracování digitálního signálu, vložený výpočetní a automatické systémy.

Pokud chcete, aby vaše operace udržovaly hladce s spolehlivou technikou, může s námi objevit objem této FPGA zajistit, abyste dostali dostupnost a konzistenci, kterou pro své projekty potřebujete.

EP1C4F324C7N CAD modely

EP1C4F324C7N Symbol

EP1C4F324C7N FOOLPRINT

EP1C4F324C7N 3D model

Funkce EP1C4F324C7N

• • Logické prvky: FPGA obsahuje 4 000 logických prvků, které umožňují efektivně implementaci složitých logických obvodů a digitálních funkcí.

• • Logické pole pole (laboratoře): Zahrnuje 400 laboratoří, které jsou základními stavebními bloky pro architekturu FPGA, což usnadňuje návrh všestranných digitálních logických konfigurací.

• • Celkové bity RAM: FPGA je vybavena 76,5 kilobity zabudovaného RAM a poskytuje zdroje paměti na čipu pro vysokorychlostní zpracování a skladování dat.

• • Počet I/O kolíků: S 249 uživatelsky konfigurovatelnými I/O kolíky podporují EP1C4F324C7N široké škálu možností propojení, přizpůsobitelné různým signálním standardům a elektronickým komponentám.

• • Provozní frekvence: Může fungovat při frekvencích až do 320 MHz, což mu umožňuje efektivně zvládnout vysokorychlostní výpočetní úkoly a procesy.

• • Napětí: Zařízení pracuje v rozsahu napájecího napětí 1,425V až 1,575 V, což zajišťuje flexibilní a spolehlivé řízení energie napříč různými aplikacemi.

• • Fázově zablokované smyčky (PLL): Vyznačuje se fázově blokovanými smyčkami pro přesné správu hodin pro načasované aplikace citlivé na načasování.

• • Podpora pro více standardů I/O: FPGA podporuje různé I/O standardy, jako jsou LVTTL, LVCMOS, SSTL-2 a SSTL-3, což zvyšuje jeho kompatibilitu s širokou škálou elektronických součástí a systémů.

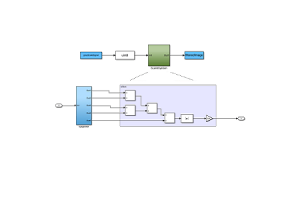

EP1C4F324C7N Block Diagram

Schéma ilustruje strukturu propojení v rámci FPGA, konkrétně odkazující na EP1C4F324C7N Zařízení ze série AlterA Cyclone.Jádrem tohoto rozložení jsou Logické bloky pole (Labs), které jsou vertikálně zarovnané moduly, které obsahují klastry logických prvků odpovědných za implementaci logických funkcí uživatelů.Každá laboratoř je připojena k sousedním laboratořům prostřednictvím přímých propojení propojení, což umožňuje vysokorychlostní komunikaci a minimalizující zpoždění šíření signálu.Tyto přímé odkazy poskytují efektivní lokalizovaný přenos dat mezi sousedními logickými bloky bez konzumace širších směrovacích zdrojů.

Obklopující laboratoře jsou dva primární typy globálních propojení: Propojení řádků a propojení sloupce.Tyto široké modré čáry slouží jako směrovací dálnice, což umožňuje signálům procházet se většími částmi tkaniny FPGA.Řádek se propojuje vodorovně, zatímco sloupec propojení běží svisle.Usnadňují spojení mezi vzdálenými logickými bloky a rozhraním se vstupními/výstupnými prvky nebo jinými funkčními jednotkami umístěnými přes čip.

Místní propojení sedí mezi laboratořemi a slouží jako přepínací látka, která překlenuje globální propojení s laboratořemi.Umožňuje logickým blokům přístup k signálům z přímých i globálních propojení.Tato směrovací hierarchie, kombinující přímé, místní, řádkové a sloupcové cesty, poskytuje flexibilní a škálovatelný přístup k distribuci signálu, optimalizaci výkonu a využití logiky v rámci EP1C4F324C7N FPGA.

Specifikace EP1C4F324C7N

|

Typ |

Parametr |

|

Výrobce |

Altera/intel |

|

Série |

Cyclone® |

|

Obal |

Podnos |

|

Stav dílu |

Zastaralý |

|

Počet laboratoří/CLB |

400 |

|

Počet logických prvků/buněk |

4000 |

|

Celkové bity RAM |

78 336 |

|

Počet I/O. |

249 |

|

Napětí - napájení |

1,425V ~ 1,575V |

|

Typ montáže |

Povrchová držák |

|

Provozní teplota |

0 ° C ~ 85 ° C (TJ) |

|

Balíček / pouzdro |

324-BGA |

|

Balíček dodavatelského zařízení |

324-FBGA (19x19) |

|

Číslo základního produktu |

EP1C4 |

Aplikace EP1C4F324C7N

Síťové zařízení

EP1C4F324C7N je vysoce vhodný pro použití v síťových zařízeních, jako jsou přepínače, směrovače a modemy.Pomáhá efektivně spravovat datový provoz, zlepšovat propustnost a snižovat latenci pro udržování vysoce výkonných síťových operací.

Průmyslová automatizace

V oblasti průmyslové automatizace lze tuto FPGA použít k řízení strojů a robotických systémů.Jeho schopnost zpracovat komplexní algoritmy rychle umožňuje řízení a monitorování, zvyšování produktivity a bezpečnosti ve výrobním prostředí.

Spotřební elektronika

EP1C4F324C7N najde aplikace ve spotřební elektronice, zejména při řízení displejů s vysokým rozlišením a správu interaktivních rozhraní v zařízeních, jako jsou inteligentní televizory a pokročilé systémy automatizace.Jeho robustní schopnosti zpracování zajišťují hladké a citlivé zážitky.

Automobilové systémy

V rámci automobilových aplikací přispívá tato FPGA k funkčnosti pokročilých systémů asistence řidiče (ADAS) a infotainmentních systémů ve vozidle.Podporuje zpracování a rozhodování o bezpečnostních a zábavních prvcích v moderních vozidlech.

Aerospace a obrana

FPGA je také použitelná v odvětví leteckých a obranných sektorů, kde zpracovává úkoly zpracování signálu a obrazu pro radarové a komunikační systémy.Díky jeho vysoké spolehlivosti a schopnosti pracovat za extrémních podmínek je ideální pro vojenské a letecké aplikace.

EP1C4F324C7N Podobné části

• • EP1C4F324C8N

• • EP1C4F324I7N

• • EP1C4F324C8

Kroky programování EP1C4F324C7N

1. Vytváření návrhu: Začněte napsáním svého designu pomocí jazyka popisu hardwaru, jako je VHDL nebo Verilog.Tento kód definuje logickou strukturu a funkci implementace hardwaru.Je důležité přesně překládat svůj hardwarový nápad do HDL, aby se zajistilo, že se FPGA chová podle očekávání.Před pokračováním v implementaci hardwaru simulujte kód HDL pomocí simulačního softwaru.Tento krok testuje logiku a funkčnost vašeho návrhu ve virtuálním prostředí, což vám umožní identifikovat a napravit chyby na začátku vývojového procesu.

2. Kompilace a syntéza : Pomocí softwaru Quartus II AlterA se kompilujte a syntetizujte svůj kód HDL.Kompilace převádí váš HDL do netlistu, obecný popis hardwaru FPGA, který mapuje váš návrh na logické prvky a směrovací prostředky.Proces montáže, součást pracovního postupu Quartus II, zahrnuje umístění a směrování vašeho designu do FPGA.Optimalizuje umístění logických prvků a směrování připojení k splnění požadavků na výkon a minimalizaci využití zdrojů.

3. Přiřazení PIN: Plánovač PIN v Quartus II umožňuje přiřadit konkrétní kolíky na FPGA vstupům a výstupům definovaným v kódu HDL.Správné přiřazení PIN je dobré pro fyzické připojení a interakci FPGA s jinými hardwarovými komponenty ve vašem systému.

4. Analýza časování: Pomocí analyzátoru časování Time Quest se ujistěte, že váš návrh splňuje požadavky na načasování.Tento nástroj kontroluje čas nastavení a držení a celkovou dobu načasování, což pomáhá předcházet problémům, jako je korupce dat a nestabilita systému.

5. Generování souborů programování: Po sestavení návrhu, syntetizovaného a ověření pro načasování, použijte nástroj Assembler v Quartus II pro vygenerování programovacího souboru.Tento soubor, obvykle s rozšířením .SOF (soubor objektu SRAM) nebo .pof (programovatelný soubor objektu), obsahuje konfigurační data pro FPGA.

6. Programování zařízení: Připojte desku FPGA k počítači pomocí rozhraní JTAG, jako je například USB-Blaster.Toto rozhraní se používá pro přenos programovacího souboru z PC do FPGA.Otevřete nástroj programátoru Quartus II pro načtení a přenosu programovacího souboru do FPGA.Tento krok nakonfiguruje FPGA s vaším návrhem, v podstatě „programování“ zařízení pro provádění požadovaných funkcí.

7. Ověření: Jakmile je FPGA naprogramována, proveďte funkční testování a ověřte, zda FPGA funguje správně podle specifikací návrhu.Toto testování může zahrnovat běh testovacích případů v laboratorním prostředí, kontrolu operací rozhraní a zajištění správného interakce FPGA s jinými hardwarovými komponenty.

Výhody EP1C4F324C7N

Flexibilita a rekonfigurabilita

EP1C4F324C7N nabízí bezkonkurenční flexibilitu ve srovnání s mikrokontroléry a ASIC, které jsou při výrobě fixovány ve své funkci.Tuto FPGA lze přeprogramovat tak, aby se přizpůsobila novým požadavkům nebo změnám v návrhu systému pro aplikace, které se v průběhu času vyvíjejí.Tato rekonfigurabilita umožňuje aktualizovat své systémy bez výměny hardwaru a zkrátit náklady i vývoj.

Schopnosti paralelního zpracování

Díky své schopnosti provádět více operací současně vyniká EP1C4F324C7N v prostředích, která vyžadují vysoce výkonný výpočet.Tato schopnost paralelního zpracování je výhodou oproti tradičním mikrokontrolérům, které fungují postupně, takže FPGA je vhodnější pro intenzivní aplikace, jako je zpracování digitálního signálu, zpracování videa a komplexní řídicí systémy.

Implementace vlastního hardwaru

FPGA umožňuje návrh vlastní hardwarové logiky přizpůsobené speciálně pro provozní potřeby uživatele.To znamená, že EP1C4F324C7N může být optimalizován pro provádění specifických úkolů efektivněji než standardní procesory nebo ASIC, což poskytuje vynikající výkon a energetickou účinnost pro specializované aplikace.

Nákladová efektivita pro nízkou až střední výrobu

U projektů, ve kterých objemy výroby neodůvodňují vysoké náklady na rozvoj ASIC, představuje EP1C4F324C7N nákladově efektivní alternativu.Poskytuje výhody přizpůsobeného hardwaru bez podstatných předem investic potřebných pro design a výrobu ASIC, což je ideální pro prototypy, malé a střední projekty nebo specializované průmyslové aplikace.

Integrace a účinnost prostoru

Schopnost integrovat více funkcí a komponent do jediného čipu FPGA činí EP1C4F324C7N vysoce cenným v prostorově omezených aplikacích.Tato integrace vede k menším, kompaktnějším návrhům zařízení, skvělému v přenosné elektronice, automobilovým aplikacím a dalším scénářům, kde je potřeba efektivita prostoru.

Rozměry balení EP1C4F324C7N

• • Typ balíčku: 324-pin jemné hřiště míčové mřížky (FBGA)

• • Velikost balíčku (Délka x šířka): 19 mm x 19 mm

• • Maximální výška sezení: 3,5 mm

• • Terminální výška: 1 mm

Výrobce EP1C4F324C7N

EP1C4F324C7N je polní programovatelné brány (FPGA) vyrobené pomocí Intel, po jejich akvizici Altery.V rámci řady Cyclone® Intel's Cyclone® představuje tato FPGA segment širokého portfolia integrovaných technologických řešení Intel.Intel, lídr v polovodičovém průmyslu, integruje pokročilé výrobní technologie a rozsáhlou podporu, aby poskytoval robustní řešení FPGA, včetně EP1C4F324C7N, který obsahuje složité logické schopnosti v kompaktním formovém faktoru.Tato FPGA zdůrazňuje závazek společnosti Intel poskytovat vysoce výkonné výpočetní komponenty, které vyhovují různým technologickým potřebám.

Závěr

Ať už vyvíjíte logiku ovládání vlastní kontroly, vytváříte vysokorychlostní komunikační systémy nebo prototypové specializované digitální funkce, EP1C4F324C7N FPGA poskytuje optimální rovnováhu výkonu, flexibility a nákladů.S jeho širokou I/O kompatibilitou, integrovanou pamětí a efektivní rekonfigurabilitou podporuje škálovatelné a prostorově efektivní návrhy napříč širokou škálou moderních aplikací.Tato FPGA, podporovaná hlavní podporou společnosti Intel, zůstává spolehlivým a přizpůsobivým řešením pro hledání robustní programovatelné logiky v nasazení nízkých i středních objemu.

DataSheet PDF

Datové listy EP1C4F324C7N:

Všechny dev Pkg Chg 1/Aug/2018.pdf

Mult Dev Dessicant CHG 19/Jul/2019.pdf

Software pro více série CHGS 26/Mar/2020.pdf

Virtual Jtag Megafuntition Guide.pdf

O nás

ALLELCO LIMITED

Přečtěte si více

Rychlý dotaz

Zašlete prosím dotaz, budeme odpovědět okamžitě.

Často kladené otázky [FAQ]

1. Lze EP1C4F324C7N použít s DDR nebo SDRAM?

Ano, tato FPGA podporuje externí typy paměti včetně DDR SDRAM, díky své více standardní podpoře I/O.Rozložení PCB však musí dodržovat přísné pokyny pro načasování a impedanci pro rozhraní vysokorychlostní paměti.

2. jaké jsou typické požadavky na výkon EP1C4F324C7N?

Toto zařízení pracuje na 1,425 V až 1,575 V jádro napětí, s dalším napětím potřebným pro I/O standardy.Pro přesné plánování napájení použijte Powerplay Powerplay Analyzer v Quartusu k odhadu spotřeby na základě vašeho návrhu.

3. Je EP1C4F324C7N ROHS kompatibilní a bez olova?

Ano, EP1C4F324C7N splňuje směrnice ROHS a je k dispozici v balíčcích bez olova.Díky tomu je vhodný pro ekologicky regulované trhy a aplikace, které vyžadují certifikaci zelené elektroniky.

4. Jak dlouho trvá kompilace a naprogramování designu na EP1C4F324C7N?

Pro mírné návrhy složitosti, kompilace a programování obvykle trvá 3 až 5 minut, v závislosti na výkonu vašeho počítače.Analýza načasování a přiřazení PIN mohou tento proces rozšířit, pokud váš návrh vyžaduje pevné omezení načasování.

5. Potřebuji nějaké speciální nástroje k programování EP1C4F324C7N?

Budete potřebovat software Intel Quartus II, který je k dispozici v bezplatném lite edici a programátorovi USB-Blaster nebo kompatibilním JTAG.Tyto nástroje vám umožňují kompilovat váš návrh, generovat programovací soubory a nahrát je do FPGA.

Procesor digitálního signálu GC5330Izev: Funkce, aplikace, alternativy a specifikace

na 2025/04/1

Kompletní průvodce rezistorem 0402: Specifikace, aplikace a pájecí techniky

na 2025/04/1

Populární příspěvky

-

Komplexní instrukční sada Počítače: Jak změnily výpočetní techniku?

na 8000/04/18 147774

-

USB-C pinout a funkce

na 2000/04/18 112017

-

Použití primitiv simulace Xilinx Unified: Komplexní průvodce designem a simulací FPGA

na 1600/04/18 111351

-

Napájecí napětí v elektronice: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/18 83771

-

Průvodce konektorem RJ45: Pinout, zapojení, typy kabelů a použití

na 1970/01/1 79568

-

Konečný průvodce barevnými kódy drátu v moderních elektrických systémech

Způsob, jakým naše elektrické systémy používají barvy, není jen pro vzhled.Každá barva drátu nyní označuje specifickou funkci, což usnadňuje správnou identifikaci a zpracování elektrických komponen...na 1970/01/1 66961

-

Průvodce čištění ventilu: funkce, příznaky, testování a náhrada za optimální výkon motoru

Vyčistit ventil je klíčovou součástí systému automobilu, který pomáhá udržovat vzduch čistý správou palivových párů, než mohou uniknout do atmosféry.To nejen pomáhá životnímu prostředí snížením zne...na 1970/01/1 63102

-

Kvalita (Q) Faktor: Rovnice a aplikace

Faktor kvality, neboli „Q“, je důležitý při kontrole toho, jak dobře induktory a rezonátory pracují v elektronických systémech, které používají rádiové frekvence (RF).„Q“ měří, jak dobře obvod mini...na 1970/01/1 63041

-

Dosažení maximálního výkonu s maximální větou přenosu energie

Maximální věta o přenosu výkonu vysvětluje, jak energie ze zdroje, jako je baterie nebo generátor, proudí do připojeného zatížení.Ukazuje přesnou podmínku, kdy zatížení přijímá nejvíce energie.Tent...na 1970/01/1 54097

-

Specifikace a kompatibilita baterie A23

Baterie A23 je malá baterie ve tvaru válce s vysokým napětím.Také se nazývá 23A, 23AE nebo MN21, běží při 12 voltech a mnohem vyšší než AA nebo AAA baterie.Díky jeho speciálnímu designu je...na 1970/01/1 52185