Průvodce EPM7256SQC208-10: Funkce, pineout, programování, aplikace a datový list

Tato příručka pojednává o EPM7256SQC208-10, typu programovatelného čipu vyrobeného společností Intel (původně Altera).Pochází z rodiny Max® 7000S a je známo, že je rychlý, spolehlivý a snadno se programoval, zatímco je již uvnitř zařízení.Tento článek vysvětluje, co čip dělá, jak to funguje, kde se používá a proč je to skvělá volba, pokud potřebujete pro váš projekt silné a flexibilní logické zařízení.Katalog

Přehled EPM7256SQC208-10

The EPM7256SQC208-10 je součástí rodiny Intel (dříve Altera) Max® 7000S, vysoce výkonný rozsah CPLD známý pro jeho robustní programovatelnost a logickou optimalizační schopnosti.Tento model se může pochlubit asi 5 000 použitelnými bran a zahrnuje 256 makrobuněk, umístěných v 208-pinovém plastovém čtyřkolku (PQFP).Pracuje na frekvenci až do 128,2 MHz a podporuje provozní napětí 5,0 V, s maximálním zpožděním šíření 7,5 ns a stropem provozní teploty +70 ° C.Klíčovou funkcí je jeho programovatelnost v systému prostřednictvím vestavěné STD IEEE.1149.1 Rozhraní JTAG, umožňující dynamickou konfiguraci.Zařízení MAX® 7000S jsou vyrobena pomocí pokročilé technologie CMOS a nabízejí funkce, jako jsou logické zpoždění pin-to-pin, jak rychle 5 ns a protimitočty dosahující až 175,4 MHz.Rodina představuje řadu možností balíčku a je navržena s programovatelnými žabky makrobuněk, které přispívají k podstatným úsporám energie nad 50% snížením některých případů.Kromě toho zahrnuje bezpečnostní bit pro ochranu proprietárních návrhů.

Pokud vaše organizace potřebuje solidní programovatelné logické řešení, EPM7256SQC208-10 je spolehlivá volba, proto nás kontaktujte ještě dnes a zajistěte svou hromadnou objednávku.

Modely EPM7256SQC208-10 CAD

Symbol EPM7256SQC208-10

Footprint EPM7256SQC208-10

EPM7256SQC208-10 3D model

Funkce EPM7256SQC208-10

• • Vysoká logická hustota: EPM7256SQC208-10 poskytuje asi 5 000 použitelných bran a obsahuje 256 makrobuněk.Díky této vysoké logické kapacitě je ideální pro implementaci komplexních kombinačních obvodů a efektivní logické integrace do kompaktních návrhů.

• • Rychlý výkon: S maximální provozní frekvencí 128,2 MHz a zpožděním šíření pouhých 7,5 ns zajišťuje tento CPLD rychlé zpracování a rychlé doby odezvy, dobré pro vysokorychlostní aplikace.

• • Programovatelnost systému (ISP): Vybaven IEEE STD.1149.1 Rozhraní JTAG, zařízení umožňuje programování a testování v systému bez nutnosti fyzického odstranění, usnadnění iteračního vývoje a aktualizací.

• • Pokročilá architektura: S využitím maximální architektury Max Adminace společnosti Altera a vyrobená s pokročilou technologií CMOS nabízí EPM7256SQC208-10 zvýšený výkon a trvanlivost, což zajišťuje spolehlivost v různých operačních prostředích.

• • Správa energie: Zařízení obsahuje programovatelné režimy šetření energie, které mohou snížit spotřebu energie o více než 50% na makrobull, podporovat energeticky účinné konstrukce a prodloužit výdrž baterie v přenosných aplikacích.

• • Bezpečnostní funkce: Programovatelný bezpečnostní bit poskytuje ochranu před neoprávněným přístupem a kopírováním proprietárních návrhů, účinně chrání duševní vlastnictví.

• • Široké provozní podmínky: Provozující při 5,0 V a schopné fungovat při teplotách až do +70 ° C, se tento CPLD přizpůsobuje různým podmínkám prostředí, což je vhodné pro průmyslové i komerční aplikace.

• • Flexibilní standardy I/O. : Podporuje operace rozhraní I/O multivolt ™ I/O, kompatibilní se systémy 3,3 V a 5,0 V.Tato flexibilita umožňuje bezproblémovou integraci s existujícím a novým hardwarem, snižuje složitost a náklady na systém.

• • Podpora návrhu: EPM7256SQC208-10 je podporována řadou nástrojů pro návrh a programování hardwarových možností, zjednodušením vývojového procesu a umožněním soustředit se spíše na inovace než na kompatibilitu.

EPM7256SQC208-10 Pinout Diagram

Tento diagram ukazuje rozložení pin pro čip EPM7256SQC208-10 od Altery.Čip má 208 kolíků, uspořádaných na všech čtyřech stranách ve čtvercovém tvaru.Pin 1 začíná v levém horním rohu a čísla kolem čipu procházejí proti směru hodinových ručiček, po levé straně k pin 53, přes dno na pin 105, po pravé straně k pin 157 a zpět do pravého horního hor.Štítky vám pomohou vědět, kde začít a jak správně umístit čip na desku obvodu.Název ve středu „EPM7256E / EPM7256S“ znamená, že toto rozvržení funguje pro obě verze čipu.Tento diagram je důležitý při připojení napájení, signálů nebo programovacích řádků k čipu.

Blokové diagram EPM7256SQC208-10

Blokový diagram EPM7256SQC208-10 ukazuje, jak je organizován čip pro zpracování digitálních logických úkolů.Má čtyři hlavní logické bloky nazývané laboratoře A, B, C a D. Každý blok obsahuje 16 makrobuněk, což jsou základní části budovy, které logickou práci provádějí.Celkem je tedy uvnitř čipu 64 makrobuněk.Kolem těchto logických bloků jsou I/O řídicí bloky, které spojují čip k vnějšímu světu prostřednictvím vstupních a výstupních kolíků.Každý kontrolní blok spravuje 6 až 16 kolíků a podle potřeby nechává signály dovnitř nebo ven z čipu.

Ve středu je programovatelné propojovací pole (PIA), které působí jako dálniční systém a umožňuje, aby signály pohybovaly mezi logickými bloky a I/O kolíky.To vám umožní směrovat data jakýmkoli způsobem, který potřebujete pro svůj návrh.Vlevo nahoře ukazuje diagram některé řídicí vstupy, jako jsou globální hodiny (GCLK), výstup Enable (OE) a Clear (GCLR).Tyto signály pomáhají řídit načasování a chování logických obvodů přes čip.

Specifikace EPM7256SQC208-10

|

Typ |

Parametr |

|

Výrobce |

Altera/intel |

|

Série |

Max® 7000s |

|

Obal |

Podnos |

|

Stav dílu |

Zastaralý |

|

Programovatelný typ |

V systému programovatelné |

|

Čas zpoždění TPD (1) Max |

10 ns |

|

Napětí napětí - interní |

4,75V ~ 5,25 V. |

|

Počet logických prvků/bloků |

16 |

|

Počet makrobuněk |

256 |

|

Počet bran |

5000 |

|

Počet I/O. |

164 |

|

Provozní teplota |

0 ° C ~ 70 ° C (TA) |

|

Typ montáže |

Povrchová držák |

|

Balíček / pouzdro |

208-BFQFP |

|

Balíček dodavatelského zařízení |

208-PQFP (28x28) |

|

Číslo základního produktu |

EPM7256 |

Aplikace EPM7256SQC208-10

Průmyslová automatizace

EPM7256SQC208-10 se rozsáhle používá v systémech průmyslové automatizace.Jeho vysoká logická hustota a rychlý výkon umožňují komplexní kontrolní úkoly, bez problémů propojí se senzory a akčními ovladami.Tento CPLD je ideální pro zvýšení přesnosti a účinnosti ve výrobních linkách, systémech řízení procesů a robotických aplikacích.

Telekomunikace

V telekomunikacích tento CPLD vyniká při správě toku dat a integrity signálu napříč sítí.Podporuje funkce, jako je konverze signálu, směrování a zpracování v přepínačích a směrovačích, což zajišťuje robustní a efektivní komunikační infrastruktury.

Automobilové systémy

V automobilovém průmyslu toto zařízení přispívá ke spolehlivosti a sofistikovanosti systémů, jako jsou jednotky pro správu motorů, infotainmentové systémy a technologie asistence řidiče.Díky jeho robustnímu výkonu za různých podmínek je vhodný pro bezpečnostní aplikace.

Zdravotnické prostředky

Přesnost a programovatelnost EPM7256SQC208-10 je cenná ve zdravotnickém vybavení, kde je důležitá přesná kontrola a spolehlivý provoz.Používá se v zařízeních pro monitorování pacientů, řízení diagnostických nástrojů a automatizaci dodávání léčby.

Aerospace a obrana

V Aerospace a obraně se EPM7256SQC208-10 používá v systémech vyžadujících vysokou úroveň spolehlivosti a výkonu, jako jsou satelitní komunikace, navigační pomůcky a vojenské kontroly hardwaru.Jeho schopnost pracovat za extrémních podmínek je prospěšná.

Vzdělávací a výzkumné instituce

Tento CPLD je také oblíbený ve vzdělávacím prostředí a výzkumných projektech, kde jeho přeprogramovatelnost a flexibilita usnadňují experimentování a učení v digitálním designu a elektronice.Umožňuje efektivně prototypovat a testovat různé logické návrhy.

Podobné části EPM7256SQC208-10

• • EPM7256ERC208-12

• • EPM7256SQC208-15

• • EPM7256EQC160-20

Kroky programování EPM7256SQC208-10

1. Zadejte režim ISP

Tento počáteční krok je důležitý, protože přechází CPLD z normálního provozního režimu do režimu programování (ISP).Toho je dosaženo odesláním konkrétního příkazu prostřednictvím rozhraní JTAG.Během tohoto procesu jsou všechny I/O kolíky CPLD tříněné (deaktivované), aby se zabránilo jakémukoli rušení nebo konfliktům s jinými složkami obvodu.Přechod do režimu ISP připravuje zařízení na bezpečné programování a trvá asi 1 milisekundu.

2. Zkontrolujte ID

Jakmile je v režimu ISP, systém provádí kontrolu ID, aby se zajistilo, že je naprogramováno správné zařízení.To zahrnuje čtení jedinečného ID zařízení silikonu prostřednictvím rozhraní JTAG.Tento krok je dobrý pro ověření, že programovací příkazy a data budou odeslány do správného zařízení, což zabrání chybnému programování a potenciálnímu poškození zařízení.

3. Hromadná vymazání

Předtím, než lze nová data naprogramovat, musí být existující data v rámci CPLD vymazána.Shromažďovací krok efektivně vyčistí všechny programovatelné buňky v zařízení.To se provádí posunutím v instrukci s vymazáním a poté použitím 100milisekundového pulsu, který vymaže celý čip.Tento krok je důležitý pro zajištění toho, aby žádné zbytky předchozích konfigurací nezasahovaly do nového programování.

4. Program

Tento krok zahrnuje skutečné programování CPLD, kde jsou do zařízení zapsána nová data konfigurace.Data a odpovídající adresy jsou přesunuty do zařízení prostřednictvím rozhraní JTAG.Každá adresa a dvojice dat vyžaduje programovací puls, aby se zajistilo, že data jsou správně zapsána do nespojených paměťových buněk CPLD.Tento krok se opakuje pro každý datový bod napříč mapou paměti zařízení.

5. Ověřte

Poprogramování je třeba ověřit, že data byla do zařízení správně zapsána.Tento krok ověřování zahrnuje čtení programovaných údajů z každé adresy a jejich porovnání s původními vstupními daty.Tento krok zajišťuje integritu dat a potvrzuje, že proces programování byl úspěšný bez jakýchkoli chyb.

6. Režim ukončení ISP

Posledním krokem v procesu programování je ukončení režimu ISP a vrácení CPLD do normálního provozního režimu.To se provádí odesláním jiného příkazu přes rozhraní JTAG.Po úspěšném odchodu jsou I/O kolíky reaktivovány a zařízení obnoví normální funkci.Tento krok také obvykle trvá asi 1 milisekundu.

Výhody EPM7256SQC208-10

Nebezpečilá konfigurace

EPM7256SQC208-10 využívá technologii EEPROM, což jí umožňuje trvale ukládat svou konfiguraci.Tato nezávislá povaha znamená, že zařízení nemusí znovu načíst svá konfigurační data z externí paměti pokaždé, když je zapnutá.To má za následek rychlejší čas spuštění a snižuje celkovou složitost návrhu hardwaru odstraněním potřeby dalších komponent pro konfiguraci.

Programovatelnost systému (ISP)

Jednou z standoutů rysů EPM7256SQC208-10 je jeho podpora programovatelnosti systému.To umožňuje, aby bylo zařízení naprogramováno a přeprogramováno, zatímco je vloženo do konečné aplikace, aniž by bylo nutné být fyzicky odstraněno.Tato schopnost zjednodušuje aktualizace a úpravy, poskytuje flexibilitu a snadné použití během vývoje a během životního cyklu produktu.

Vysoký počet I/O a logická hustota

Zařízení nabízí značné množství logických zdrojů a I/O pinů s 256 makrobuněk a 164 uživatelskými I/O kolíky.Tento vysoký počet I/O a logická hustota umožňuje integraci více funkcí do jediného čipu, což usnadňuje složitější návrhy a zároveň zachovává prostor na PCB.Tato výhoda je prospěšná v aplikacích, kde je prostor na desce na prémii a je důležitá multifunkčnost.

Rychlé zpoždění na pin

S maximálním zpožděním pin-to-pin pouhých 10 ns může EPM7256SQC208-10 provádět vysokorychlostní logické operace.Tato rychlá doba odezvy je skvělá v aplikacích, které vyžadují rychlé schopnosti zpracování, jako je vysokorychlostní komunikace nebo výpočetní technika, což zajišťuje, že systém splňuje přísná kritéria výkonu.

Kompatibilita širokého napětí

EPM7256SQC208-10 je navržen tak, aby byl flexibilní, pokud jde o kompatibilitu napětí, podporuje vnitřní provoz při 5 V a I/O hladinách při 3,3 V. Tato schopnost duálního napětí umožňuje snadno propojit se systémy 3,3 V a 5 V, což snižuje potřeba překladačů na vozidle a zjednodušit návrh systému.

Rozměry balení EPM7256SQC208-10

• • Typ balíčku: 208-BFQFP (plastový čtyřkolek)

• • Počet kolíků: 208 vedení

• • Velikost těla (L × W): 28 mm × 28 mm

• • Styl montáže: Technologie montáže na povrch (SMT)

• • Hřiště olova: Obvykle 0,5 mm mezi kolíky (standard pro BFQFP)

• • Balíček materiál: Plast

• • Tloušťka balíčku: Přibližně 3,5 mm (liší se mírně podle výrobce)

• • Tepelné charakteristiky: Žádná exponovaná podložka;Standardní rozptyl okolního okolí přes desku

• • Balení podnos: Dodáváno v zásobnících pro manipulaci s objemem a automatizaci pick-and-místo

Výrobce EPM7256SQC208-10

EPM7256SQC208-10 byl původně vyvinut a vyroben pomocí Altera Corporation, přední průkopník v programovatelných logických zařízeních známý pro svou řadu CPLD Max® 7000S.V roce 2015 byla Altera získána společností Intel Corporation, jeden z největších světových polovodičových výrobců.Od akvizice společnost Intel nadále podporovala a integrovala společnost CPLD a FPGA Technologies AlterA v rámci skupiny programovatelných řešení.EPM7256SQC208-10 představuje dědictví Intel v nabídce vysoce výkonných, programovatelných logických řešení v systému přizpůsobená pro širokou škálu průmyslových, telekomunikačních a zabudovaných aplikací.Ačkoli je nyní klasifikována jako zastaralá, část odráží dlouhodobý závazek společnosti Intel k spolehlivým a flexibilním programovatelným logickým zařízením.

Závěr

EPM7256SQC208-10 je chytrý a spolehlivý čip, který pomáhá hladce běžet digitální systémy.Ušetří energii, podporuje různá napětí a umožňuje vám ji naprogramovat, když je již nainstalována, což usnadňuje aktualizace.I když je to nyní starší čip, jiní jej stále používají, protože to funguje dobře ve všech druzích systémů.Pokud potřebujete solidní čip pro kontrolu logiky ve vašem návrhu, je tento skvělou volbou.Kontaktujte nás ještě dnes, pokud si to chcete objednat hromadně.

DataSheet PDF

Datové listy EPM7256SQC208-10:

Softwarový disk 06/Nov/2020.pdf

O nás

ALLELCO LIMITED

Přečtěte si více

Rychlý dotaz

Zašlete prosím dotaz, budeme odpovědět okamžitě.

Často kladené otázky [FAQ]

1. Jaké programovací nástroje jsou kompatibilní s EPM7256SQC208-10?

Můžete použít software Quartus II (dříve Altera Quartus) spolu s programátorem kompatibilním s JTAG, jako je USB-Blaster, k konfiguraci a naprogramování EPM7256SQC208-10 přímo v systému.

2. mohu přeprogramovat EPM7256SQC208-10 několikrát?

Ano, EPM7256SQC208-10 podporuje několik cyklů přeprogramování pomocí programovatelnosti v systému založené na EEPROM, což je ideální pro iterativní vývoj designu nebo aktualizace po nasazení.

3. Může EPM7256SQC208-10 zvládnout drsné provozní podmínky?

Spolehlivě pracuje v komerčním teplotním rozmezí 0 ° C až +70 ° C, což je dostatečné pro většinu průmyslových a zabudovaných aplikací, i když ne pro extrémní nebo automobilové prostředí.

4. mohu stále naprogramovat EPM7256SQC208-10, aniž bych jej odstranil z desky obvodu?

Ano.Chip podporuje programovatelnost v systému (ISP) prostřednictvím JTAG, což vám umožňuje přeprogramovat jej, zatímco je již připáleno na vaši desku, šetří čas a úsilí během vývoje nebo údržby.

5. Co dělá EPM7256SQC208-10 lepší než standardní mikrokontrolér pro logické úkoly?

Na rozdíl od mikrokontrolérů je EPM7256SQC208-10 CPLD, který vyniká při provádění paralelních logických operací s přesným načasováním.Je to ideální, když potřebujete rychle, deterministickou digitální kontrolu nad více signály.

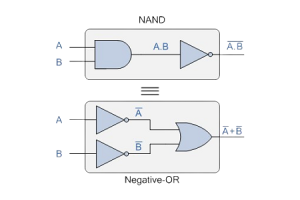

Demorganovy věty vysvětlily: Zjednodušení logických výrazů pro lepší návrh obvodu

na 2025/04/25

Základy a příklady obvodu Norton THEOREM

na 2025/04/24

Populární příspěvky

-

Komplexní instrukční sada Počítače: Jak změnily výpočetní techniku?

na 8000/04/18 147769

-

USB-C pinout a funkce

na 2000/04/18 111996

-

Použití primitiv simulace Xilinx Unified: Komplexní průvodce designem a simulací FPGA

na 1600/04/18 111351

-

Napájecí napětí v elektronice: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/18 83765

-

Průvodce konektorem RJ45: Pinout, zapojení, typy kabelů a použití

na 1970/01/1 79555

-

Konečný průvodce barevnými kódy drátu v moderních elektrických systémech

Způsob, jakým naše elektrické systémy používají barvy, není jen pro vzhled.Každá barva drátu nyní označuje specifickou funkci, což usnadňuje správnou identifikaci a zpracování elektrických komponen...na 1970/01/1 66956

-

Průvodce čištění ventilu: funkce, příznaky, testování a náhrada za optimální výkon motoru

Vyčistit ventil je klíčovou součástí systému automobilu, který pomáhá udržovat vzduch čistý správou palivových párů, než mohou uniknout do atmosféry.To nejen pomáhá životnímu prostředí snížením zne...na 1970/01/1 63098

-

Kvalita (Q) Faktor: Rovnice a aplikace

Faktor kvality, neboli „Q“, je důležitý při kontrole toho, jak dobře induktory a rezonátory pracují v elektronických systémech, které používají rádiové frekvence (RF).„Q“ měří, jak dobře obvod mini...na 1970/01/1 63029

-

Dosažení maximálního výkonu s maximální větou přenosu energie

Maximální věta o přenosu výkonu vysvětluje, jak energie ze zdroje, jako je baterie nebo generátor, proudí do připojeného zatížení.Ukazuje přesnou podmínku, kdy zatížení přijímá nejvíce energie.Tent...na 1970/01/1 54095

-

Specifikace a kompatibilita baterie A23

Baterie A23 je malá baterie ve tvaru válce s vysokým napětím.Také se nazývá 23A, 23AE nebo MN21, běží při 12 voltech a mnohem vyšší než AA nebo AAA baterie.Díky jeho speciálnímu designu je...na 1970/01/1 52177