EPM7192SQC160-15 CPLD: Funkce, pineout, programování a aplikace

Tato příručka hovoří o EPM7192SQC160-15, programovatelném logickém čipu z rodiny Max 7000s.Vysvětluje to, co může čip udělat, jak to funguje a kde jej lze použít.Ukazuje, jak je čip postaven uvnitř, co každý kolík dělá a jak se připojuje k jiným částem.Průvodce také zahrnuje tam, kde lze tento čip použít, jak jej programovat krok za krokem, jaké další podobné čipy existují a kdo to dělá.Katalog

Co je to EPM7192SQC160-15?

The EPM7192SQC160-15 je střední třída CPLD (komplexní programovatelné logické zařízení) z rodiny Max 7000s, která je vytvořena pro spolehlivé digitální logické ovládání v vestavěných a průmyslových systémech.Tento čip nabízí 192 makrobuněk a asi 3 750 logických bran, což poskytuje dostatečnou kapacitu pro manipulaci s mírnými logickými úkoly.Zahrnuje 124 I/O kolíků a běží na dodávce 5V, s podporou více I/O pro rozhraní s logickými systémy 3,3V a 5V.Jeho in-systému programovatelná architektura založená na EEPROM znamená, že ji můžete přeprogramovat přímo do svého obvodu pomocí JTAG, aniž byste potřebovali další komponenty nebo externí paměť.S rychlostní stupeň –15 podporuje frekvence systémových hodin do asi 76,9 MHz, což nabízí rychlý a konzistentní načasovací výkon pro rozsáhlé digitální aplikace.Rodina Max 7000s je známá svým solidním výkonem, pamětí EEPROM a flexibilním napětím.

Hledáte EPM7192SQC160-15?Kontaktujte nás a zkontrolujte aktuální zásoby, dodací lhůtu a ceny.

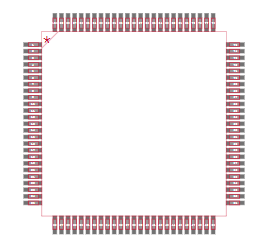

Modely EPM7192SQC160-15 CAD

Symbol EPM7192SQC160-15

EPM7192SQC160-15 Footprint

EPM7192SQC160-15 3D model

Funkce EPM7192SQC160-15

192 makrocells: Zařízení zahrnuje 192 makrobuněk, které slouží jako základní programovatelné prvky.Tyto makrobuněk lze nakonfigurovat pro implementaci široké škály kombinačních a sekvenčních logických funkcí potřebných v digitálních návrzích.

Přibližně 3 750 logických bran: Nabízí ekvivalentní logickou kapacitu přibližně 3 750 bran, díky čemuž je vhodná pro logiku ovládání střední slovy, stavové stroje nebo logiku lepidla v zabudovaných systémech.

Programovatelnost systému prostřednictvím JTAG: Je vybaven pamětí založenou na EEPROM, která umožňuje přeprogramování přímo v systému pomocí standardního rozhraní JTAG a podporuje standardy IEEE 1149.1 a IEEE 1532.

Maximální frekvence do 125 MHz: Interní logika může pracovat při rychlostech hodin dosahujících 125 MHz, což umožňuje rychlé zpracování pro načasování citlivé aplikace.

Zpoždění šíření 7,5 ns: Čip nabízí nízké zpoždění šíření přibližně 7,5 nanosekund, což zajišťuje rychlou odezvu signálu ze vstupu na výstup.

Podporuje 5V dodávky s více I/O více i/o: Zařízení běží na dodávce jádra 5V a podporuje multivoltové I/O, což umožňuje kompatibilitu s úrovněmi signálu 5V a 3,3 V pro snadnou integraci do systémů smíšeného napětí.

Programovatelná rychlost proudění a výstupy s otevřeným odtokem: Můžete řídit rychlosti okraje signálu pro redukci EMI a vybrat výstupy s otevřeným odtokem pro posun kabelových a logických nebo logických nebo úrovně.

Šest globálních výstupů Povolte signály: Tyto globální kontrolní signály umožňují umožnit nebo deaktivovat výstupy napříč více I/O bankami pro efektivní správu signálu.

Konfigurovatelné žabky v makrobulkách: Každé makrocell obsahuje flip-flop, který podporuje předvolbu, jasné, hodiny povolení a individuální kontrolu, což poskytuje zvýšenou flexibilitu pro sekvenční logický design.

Režim nízkého výkonu: Zařízení obsahuje funkci úspory energie, která může snížit spotřebu energie makrobuněk o více než 50%, což je prospěšné pro energeticky účinné aplikace.

Podpora testu na hranici JTAG : Zařízení s 128 nebo více makrobuněk, jako je tato, zahrnují úplné funkce testování mezních skenování pro efektivní diagnostiku a validaci na úrovni desky.

Bezpečnostní bit pro ochranu návrhu: Programovatelný bezpečnostní bit zajišťuje, že interní design nelze číst nebo zkopírovat a chránit duševní vlastnictví.

I/O kompatibilní s PCI: Struktura I/O je navržena tak, aby splňovala elektrické požadavky PCI, což umožňuje přímé propojení se systémy založenými na PCI.

Rozsah provozní teploty 0 ° C až 70 ° C: Standardní teplotní rozsah komerčního stupně způsobuje, že toto zařízení je vhodné pro většinu aplikací pro vnitřní a kontrolované prostředí.

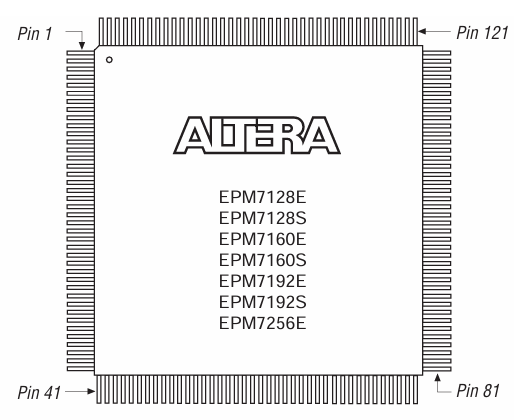

EPM7192SQC160-15 Pinout Diagram

Tento diagram ukazuje rozložení pin pro EPM7192SQC160-15 a podobná zařízení Max 7000s.Čip má 160 kolíků uspořádaných kolem všech čtyř stran v balíčku čtvercového QFP.Pin 1 začíná v levém levém rohu a čísla se pohybují proti směru hodinových ručiček kolem čipu.Každá strana má 40 kolíků.Malá tečka v levém horním značce Pin 1, což pomáhá při správném umístění.Název čipu ve středu ukazuje, že je kompatibilní s jinými modely ve stejné rodině.Toto rozvržení poskytuje mnoho I/O připojení a je užitečné pro komplexní logické návrhy.

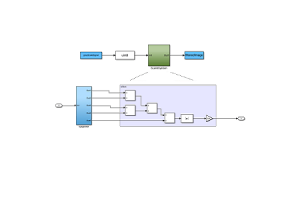

Blok Schéma max. 7000S

Tento blokový diagram ukazuje vnitřní strukturu CPLD Max 7000S, včetně EPM7192SQC160-15.Čip je rozdělen do čtyř hlavních sekcí nazývaných bloky logického pole (laboratoř A až d).Každá laboratoř má 16 makrobuněk, což jsou malé logické jednotky používané k vytváření digitálních obvodů.Společně tyto laboratoře zpracovávají složité logické operace.

Ve středu je programovatelné pole propojení (PIA), které spojuje všechny laboratoře a umožňuje jim sdílet data.Každá laboratoř posílá a přijímá signály prostřednictvím 36 kanálů, což poskytuje flexibilní směrování mezi logickými bloky.Kolem okrajů existují I/O řídicí bloky, které propojují 6 až 16 I/O kolíků s každou laboratoří, což umožňuje zařízení propojit s jinými částmi systému.

Nahoře jsou zobrazeny globální kontrolní signály, jako jsou hodiny a výstup.Tyto signály pomáhají zvládat, jak se data pohybují uvnitř čipu a kdy jsou výstupy aktivní.Celkově diagram ukazuje, jak EPM7192SQC160-15 organizuje svou logiku a připojení k podpoře vlastních digitálních návrhů.

Specifikace EPM7192SQC160-15

|

Typ |

Parametr |

|

Výrobce |

Altera |

|

Série |

Max® 7000s |

|

Obal |

Podnos |

|

Stav dílu |

Zastaralý |

|

Programovatelný typ |

V systému programovatelné |

|

Čas zpoždění TPD (1) Max |

15 ns |

|

Napětí napětí - interní |

4,75V ~ 5,25 V. |

|

Počet logických prvků/bloků |

12 |

|

Počet makrobuněk |

192 |

|

Počet bran |

3750 |

|

Počet I/O. |

124 |

|

Provozní teplota |

0 ° C ~ 70 ° C (TA) |

|

Typ montáže |

Povrchová držák |

|

Balíček / pouzdro |

160-bqfp |

|

Balíček dodavatelského zařízení |

160-PQFP (28x28) |

|

Číslo základního produktu |

EPM7192 |

Aplikace EPM7192SQC160-15

Logika lepidla vestavěného systému

EPM7192SQC160-15 je ideální pro překlenutí různých digitálních zařízení ve vestavěných systémech.Lze jej použít ke správě komunikace mezi mikrokontroléry, paměťovými čipy a I/O zařízeními zpracováním adresy dekódováním, ovládáním sběrnice a úpravy načasování, aniž by bylo nutné diskrétní logiky.

Stav stroje a kontrolní logika

S jeho 192 makrobuněk je čip vhodný pro implementaci vlastních strojů a logiky kontroly.Běžně se používá při automatizačních úkolech, motorických ovladačích a řídicích systémech založených na načasování, které vyžadují spolehlivé a opakovatelné přechody stavu.

Rozhraní komunikačního protokolu

Tento CPLD lze naprogramovat tak, aby vytvořil nebo překládal komunikační protokoly, jako jsou UART, SPI, I²C nebo vlastní sériové formáty.Umožňuje snadnou konfiguraci a úpravu bez změny hardwaru, což je cenné pro propojení komunikace.

Předběžné zpracování digitálního signálu

Díky své rychlé logické rychlosti a nízkému zpoždění šíření dokáže zvládnout jednoduché úkoly zpracování signálu, jako je filtrování, multiplexování nebo detekce okrajů, než signály dosáhnou hlavního procesoru nebo čipu DSP.

Překlad rozhraní a řazení úrovně

Jeho schopnost multivolt I/O podporuje signály 3,3V a 5V.Díky tomu je vhodný pro návrhy, které zahrnují komponenty pracující na různých úrovních napětí, což umožňuje bezpečný a efektivní překlad napětí.

Rychlé prototypování a aktualizace in-systému

Tento čip můžete použít v systémech, které mohou vyžadovat časté logické aktualizace.Jeho struktura založená na EEPROM a programovací rozhraní JTAG umožňují přeprogramovat logiku i po sestavení desky.

Testovací a diagnostika na úrovni desky

S podporou hraniční skenování prostřednictvím JTAG testuje spojení mezi čipy na PCB bez potřeby sond.To je užitečné při výrobě a diagnostice v terénu pro detekci problémů s pájení nebo směrování.

Podobné části EPM7192SQC160-15

• • EPM7192EQC160-20 (Altera)

Toto zařízení pochází ze stejné řady Max 7000 a nabízí stejné logické zdroje, 192 makrobuněk a 124 I/O kolíků v 160-pinovém balíčku PQFP.Funguje v pomalejším rychlostním stupni –20, což znamená, že má delší zpoždění šíření (~ 20 ns), ale stále splňuje potřeby nelikčních návrhů.Je to vhodná alternativa pro aplikace, kde je důležitá logická hustota, ale ultra rychlé načasování není prioritou, což je ideální pro nákladné projekty, které stále vyžadují funkční rovnocennost.

• • EPM7192SQI160-10N (Altera)

Tato část je také logicky kompatibilní s EPM7192SQC160-15 a nabízí stejný počet makrobuněk a I/OS.Používá však rychlostní stupeň –10, která podporuje rychlejší provoz se zlepšeným načasováním (zpoždění šíření 10 ns).Podporuje také prodloužený teplotní rozsah od –40 ° C do +85 ° C, což z něj činí vynikající náhradu za průmyslové nebo outdoorové aplikace.Díky tomu je ideální, když je vyžadována vyšší rychlost a odolnost životního prostředí.

• • EPM7192SQC160-7 (Intel)

Jako přímá varianta zrychlení EPM7192SQC160-15 přináší verze –7 nejrychlejší výkon v rodině, přičemž šíření zpožďuje až 7,5 ns.Udržuje stejnou konfiguraci kolíku, specifikace napájení a logickou hustotu a nabízí výměnu drop-in pro ty, kteří hledají lepší rychlost bez změny rozvržení desky nebo napětí.Díky tomu je nejlepší volba pro načasování kritických návrhů, které potřebují rychlejší odezvu signálu a zároveň zůstanou ve stejné stopě designu.

Kroky programování EPM7192SQC160-15

1. Zadejte režim ISP

Prvním krokem je přesun zařízení do režimu ISP (programování v rámci systému).To se provádí prostřednictvím rozhraní JTAG.Jakmile jsou v režimu ISP, všechny I/O kolíky na zařízení jsou umístěny do bezpečného režimu Tri-State, aby se zabránilo nezamýšlené logické rušení během programování.Tato inicializace obvykle trvá asi 1 milisekundu.

2. Zkontrolujte ID zařízení

Do zařízení je vloženo jedinečné ID křemíku pro ověření, že se jedná o správný model před zahájením programování.Systém se posouvá v instrukci pro čtení a načte ID přes linku TDO (testovací data).Tato kontrola zajišťuje, že programovací nástroj je připojen k pravému CPLD a vyhýbá se chybám, jako je přepsání jiné části.

3. Hromadná vymazání

Hromadná vymazání vymaže všechna dříve uložená data v paměti EEPROM na CPLD.Tím se připravuje čip k přijetí nové konfigurace.Mazací příkaz iniciuje puls, který obvykle trvá asi 100 milisekund, což zajišťuje resetování všech programovatelných buněk.

4. Program EEPROM

Nová konfigurační data jsou načtena do zařízení posunutím adresy a datových bitů přes port JTAG.Každá paměťová buňka je napsána jeden po druhém s programovacím pulsem aplikovaným po každém úspěšném cyklu zápisu.Tento proces definuje logickou strukturu, kterou CPLD použije při napájení.

5. Ověřte EEPROM

Po programování zařízení provádí krok ověření.To zahrnuje čtení zpět každé programované polohy paměti a porovnání výstupních hodnot s zamýšlenými daty.Pokud ověření selže, musí být proces opakován.Tento krok zaručuje, že konfigurace byla úspěšně napsána.

6. Režim ukončení ISP

Jakmile je ověření dokončeno, je vydán konečný příkaz k ukončení ISP režimu.Zařízení reaktivuje své I/O kolíky a obnoví normální provoz.Tento přechod také trvá asi 1 milisekundu a dokončí cyklus programování v systému.

EPM7192SQC160-15 Rozměry balení

• • Velikost těla: 28 mm × 28 mm

• • Výška balíčku: 3,4 mm

• • Pitch Pitch: 0,65 mm

Výrobce EPM7192SQC160-15

EPM7192SQC160-15 byl původně vyroben společností Altera Corporation, společnost známá svými pokročilými programovatelnými logickými zařízeními.V roce 2015 byla Altera získána společností Intel Corporation, a zařízení je nyní součástí skupiny programovatelných řešení společnosti Intel pod rodinou CPLD Max 7000s.Intel nadále podporuje Legacy Altera produkty, ačkoli EPM7192SQC160-15 je nyní ve většině oficiálních katalogů klasifikován jako zastaralý.Navzdory svému ukončenému statusu zajišťuje historická reputace společnosti Intel pro spolehlivost a dědictví Altery ve vysoce výkonných logických řešeních prostřednictvím sekundárních distributorů pokračující poptávka a dostupnost.

Závěr

EPM7192SQC160-15 je užitečný a flexibilní čip pro manipulaci s digitálními ovládacími úkoly v mnoha elektronických systémech.Nabízí dostatek logické síly pro úlohy, jako je budování vlastních stavových strojů, manipulační signály a připojení různých zařízení.Podporuje různé úrovně napětí, funguje rychlými rychlostmi a lze jej snadno aktualizovat prostřednictvím JTAG.Jeho vnitřní design umožňuje hladký průtok signálu a snadné změny logiky.Přestože je nyní přerušen, je to stále skvělá volba pro staré nebo probíhající projekty a lze jej nahradit podobnými čipy, které nabízejí rychlejší nebo širší podporu teploty.

DataSheet PDF

Datové listy EPM7192SQC160-15:

O nás

ALLELCO LIMITED

Přečtěte si více

Rychlý dotaz

Zašlete prosím dotaz, budeme odpovědět okamžitě.

Často kladené otázky [FAQ]

1. Mohu naprogramovat EPM7192SQC160-15, aniž bych jej odstranil z desky obvodu?

Ano, čip podporuje programování in-systému (ISP) prostřednictvím rozhraní JTAG, takže jej můžete programovat nebo přeprogramovat přímo, když je pájena na PCB, což zjednodušuje aktualizace designu a snižuje přepracování.

2. jaký programovací software bych měl použít pro EPM7192SQC160-15?

Software Quartus II (starší verze) můžete použít k vytvoření logických návrhů, kompilaci kódu a správu programovacího procesu založený na JTAG.Quartus II podporuje zařízení Max 7000S, jako je EPM7192SQC160-15.

3. Vyžaduje EPM7192SQC160-15 pro provoz externí paměť?

Ne, má interní konfigurační paměť založenou na EEPROM.Veškerá logická konfigurace je uložena uvnitř čipu, takže pro ukládání logických stavů nebo sekvencí zavádění není nutná žádná externí paměť.

4. Co dělá EPM7192SQC160-15 vhodný pro průmyslové použití?

Díky jeho robustní operaci 5V, kompatibilita I/O multivolt, rychlé logické zpracování a netěsnitelnou paměť založenou na EEPROM jsou spolehlivé pro průmyslové systémy, které vyžadují stabilní a odolné digitální logické funkce.

5. Jak zpracovává EPM7192SQC160-15 systémy smíšeného napětí?

Díky své podpoře I/O se zařízením může zařízení propojit jak s úrovněmi 3,3V, tak 5V, což je ideální pro systémy smíšeného signálu a propojení s moderními nízkonapěťovými komponenty.

Proč pro svůj projekt zvolit EPF10K100EFC484-3

na 2025/06/13

Co je přepínač SPST a jak to funguje?

na 2025/06/12

Populární příspěvky

-

Komplexní instrukční sada Počítače: Jak změnily výpočetní techniku?

na 8000/04/18 147760

-

USB-C pinout a funkce

na 2000/04/18 111969

-

Použití primitiv simulace Xilinx Unified: Komplexní průvodce designem a simulací FPGA

na 1600/04/18 111351

-

Napájecí napětí v elektronice: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/18 83734

-

Průvodce konektorem RJ45: Pinout, zapojení, typy kabelů a použití

na 1970/01/1 79522

-

Konečný průvodce barevnými kódy drátu v moderních elektrických systémech

Způsob, jakým naše elektrické systémy používají barvy, není jen pro vzhled.Každá barva drátu nyní označuje specifickou funkci, což usnadňuje správnou identifikaci a zpracování elektrických komponen...na 1970/01/1 66932

-

Průvodce čištění ventilu: funkce, příznaky, testování a náhrada za optimální výkon motoru

Vyčistit ventil je klíčovou součástí systému automobilu, který pomáhá udržovat vzduch čistý správou palivových párů, než mohou uniknout do atmosféry.To nejen pomáhá životnímu prostředí snížením zne...na 1970/01/1 63084

-

Kvalita (Q) Faktor: Rovnice a aplikace

Faktor kvality, neboli „Q“, je důležitý při kontrole toho, jak dobře induktory a rezonátory pracují v elektronických systémech, které používají rádiové frekvence (RF).„Q“ měří, jak dobře obvod mini...na 1970/01/1 63025

-

Dosažení maximálního výkonu s maximální větou přenosu energie

Maximální věta o přenosu výkonu vysvětluje, jak energie ze zdroje, jako je baterie nebo generátor, proudí do připojeného zatížení.Ukazuje přesnou podmínku, kdy zatížení přijímá nejvíce energie.Tent...na 1970/01/1 54090

-

Specifikace a kompatibilita baterie A23

Baterie A23 je malá baterie ve tvaru válce s vysokým napětím.Také se nazývá 23A, 23AE nebo MN21, běží při 12 voltech a mnohem vyšší než AA nebo AAA baterie.Díky jeho speciálnímu designu je...na 1970/01/1 52163