EPM7064STC100-7 CPLD: Průvodce programováním v oblasti programování

EPM7064STC100-7 je výkonný čip ze série Intel Max® 7000S, který je navržen tak, aby zpracovával složité úkoly v elektronických zařízeních.Tato příručka pojednává o hlavních rysech a použití EPM7064STC100-7 a zdůrazňuje jeho schopnost být snadno přeprogramována, její rychlý provoz a jeho flexibilní design.Tento čip je ideální pro mnoho různých technologií, od malých pomůcek po velké průmyslové stroje, klíčovým kusem pro budování pokročilých digitálních obvodů.Katalog

EPM7064STC100-7 Popis

The EPM7064STC100-7 je komplexní programovatelné logické zařízení (CPLD) ze série Intel Max® 7000S.Má 64 makrobuněk a 1 250 bran, které pomáhají při vytváření složitých digitálních obvodů.Tento čip probíhá při maximální rychlosti 166,7 MHz, se zpožděním signálu 7,5 nanosekundy (NS).Má 68 vstupních/výstupů (I/O) kolíků, které pracují s logikou 3,3V a 5V, což usnadňuje použití v různých obvodech.Klíčovým prvkem je jeho 5,0V programovatelnost (ISP) prostřednictvím rozhraní JTAG (IEEE 1149.1).To znamená, že jej můžete přeprogramovat bez jeho odebrání z obvodu, což usnadňuje testování a aktualizace.Je dodáván ve 100kolíkovém Quad Flat Pack (TQFP), což je kompaktní balíček povrchu.Tento CPLD se používá ve vestavěných systémech, zpracování digitálních signálů, komunikačních zařízeních a průmyslové automatizaci.

Poskytujeme vysoce kvalitní komponenty a přizpůsobené služby, takže je nejlepší s námi zadat svou hromadnou objednávku pro spolehlivá řešení CPLD.

Funkce EPM7064STC100-7

• • Logika s vysokou hustotou: EPM7064STC100-7 je navržen s 64 makrobuněk a 1 250 použitelnými bran, což je velmi vhodné pro implementaci složitých logických funkcí v digitálních obvodech.Tato architektura s vysokou hustotou umožňuje vytvářet složité logické návrhy při zachování účinnosti programovatelných logických operací.Dobře optimalizovaná struktura makrobuněk zajišťuje účinné využití dostupných zdrojů a podporuje pokročilé kombinační a sekvenční logické implementace.

• • Rychlý výkon: EPM7064STC100-7, postavený pro vysokorychlostní zpracování, pracuje s maximální vnitřní frekvencí 166,7 MHz, což umožňuje rychlé provádění logických funkcí.Jeho zpoždění šíření 7,5 ns zajišťuje minimální latenci.Tato schopnost rychlého přepínání zvyšuje schopnost zařízení zvládnout vysokorychlostní zpracování dat, kondicionování signálu a kontrolu efektivně, což z něj činí spolehlivou volbu pro náročné digitální systémy.

• • Všestranný I/O: S 68 programovatelnými vstupními/výstupnými kolíky nabízí EPM7064STC100-7 výjimečnou flexibilitu pro integraci do různých návrhů obvodů.Podpora logických úrovní 3,3 V a 5V umožňuje bezproblémovou kompatibilitu s různými systémovými napětími, což eliminuje potřebu dalšího řazení úrovně napětí.Díky této přizpůsobivosti je vhodný pro aplikace v prostředí smíšeného napětí a zajišťuje širokou použitelnost napříč zabudovanými systémy, průmyslovými ovládacími prvky a komunikačními sítěmi.

• • Programovatelnost systému (ISP): Jednou z výhod EPM7064STC100-7 je její 5,0V programovatelnost (ISP), usnadněná prostřednictvím IEEE STD.1149.1 Rozhraní JTAG.Tato funkce umožňuje přeprogramovat a modifikovat logické funkce bez denold nebo fyzického odstranění zařízení, zjednodušit údržbu, ladění a iterační vývoj.Schopnost ISP snižuje prostoje a zvyšuje flexibilitu aktualizací firmwaru, což je neocenitelné pro dynamické a rekonfigurovatelné digitální návrhy.

EPM7064STC100-7 CAD modely

EPM7064STC100-7 Symbol

EPM7064STC100-7 FOOLPRINT

EPM7064STC100-7 3D model

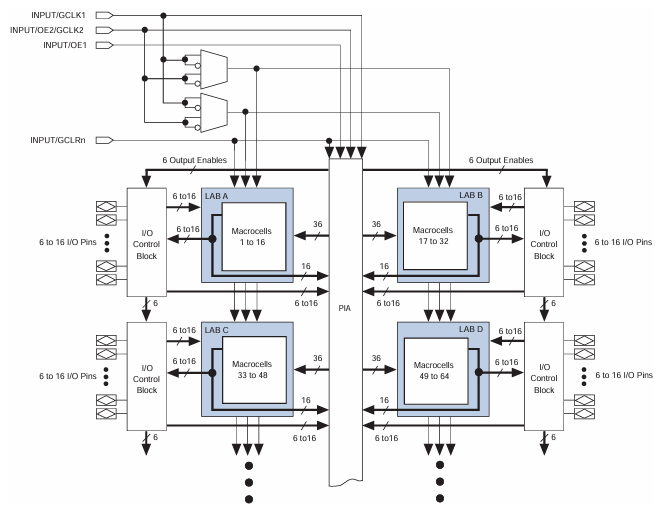

EPM7064STC100-7 Blokové diagram

The EPM7064STC100-7 Blokové diagram ukazuje, jak jsou logické prvky čipu připojeny a kontrolovány.Má čtyři bloky logického pole (laboratoře), označené A, B, C a D, z nichž každá obsahuje 16 makrobuněk.Tyto makrobuněk provádějí logické funkce a propojují se prostřednictvím programovatelného propojovacího pole (PIA), které umožňuje flexibilní směrování signálů.Každá laboratoř je propojena s I/O řídicím blokem, manipulace až 16 vstupních/výstupních kolíků na laboratoř.Schéma také zobrazuje globální kontrolní signály (GCLK1, GCLK2, OE1 a GCLRN), které pomáhají spravovat funkce taktování a resetování pro čip.Některé logické brány zpracovávají tyto signály dříve, než dosáhnou různých částí systému.Konstrukce EPM7064STC100-7 umožňuje jeho použití v různých programovatelných logických aplikacích, jako jsou státní stroje, dekódování adresy a další vlastní digitální obvody.Jeho flexibilní propojení zajišťují efektivní tok signálu a spolehlivé provoz.

Specifikace EPM7064STC100-7

|

Typ |

Parametr |

|

Výrobce |

Altera/intel |

|

Série |

Max® 7000s |

|

Obal |

Podnos |

|

Stav dílu |

Zastaralý |

|

Programovatelný typ |

V systému programovatelné |

|

Čas zpoždění TPD (1) Max |

7,5 ns |

|

Napětí napětí - interní |

4,75V ~ 5,25 V. |

|

Počet logických prvků/bloků |

4 |

|

Počet makrobuněk |

64 |

|

Počet bran |

1250 |

|

Počet I/O. |

68 |

|

Provozní teplota |

0 ° C ~ 70 ° C (TA) |

|

Typ montáže |

Povrchová držák |

|

Balíček / pouzdro |

100-TQFP |

|

Balíček dodavatelského zařízení |

100-TQFP (14x14) |

|

Číslo základního produktu |

EPM7064 |

EPM7064STC100-7 SESTENCE SYSTÉMOVÁNÍ (ISP)

EPM7064STC100-7, část rodiny CPLD Max 7000S, se řídí šestistupňovou sekvencí programování (ISP), aby byla zajištěna správná konfigurace.Tento proces umožňuje programovat zařízení bez jeho odebrání z desky obvodu.Proces ISP zahrnuje posouvání pokynů, adres a dat prostřednictvím PIN TDI (testovací data) při získávání odpovědí prostřednictvím PIN TDO (testovací data).

První fáze, Zadejte ISP, zajišťuje, že I/O kolíky hladce přecházejí z uživatelského režimu do režimu ISP a vyžadují přibližně 1 mms.Poté následuje Zkontrolujte ID, kde je čtení ID křemíku zařízení pro potvrzení správného cíle.Dále, Hromadná vymazání Posuny fáze v vymazání pokynů a aplikují 100ms vymazaný puls a vyčistí všechna existující data v buňkách EEPROM.The Naprogramovat Následuje fáze, kde jsou adresy a data postupně přesunuty do zařízení a aplikují programovací impulzy pro konfiguraci buněk EEPROM.Každá adresa musí být naprogramována jednotlivě, takže tento krok je časově náročný v závislosti na počtu buněk EEPROM v zařízení.

Jakmile je programování dokončeno, Ověřit Fáze zajišťuje, že data byla správně uložena.Zde jsou na Eeprom buňky aplikovány číst pulzy a získaná data jsou porovnána s očekávanými hodnotami.Jsou -li nalezeny nesrovnalosti, může být nutné přeprogramování.Nakonec Ukončení ISP Fáze zajišťuje, že I/O kolíky přecházejí zpět do uživatelského režimu, což vyžaduje další 1ms.Celková doba programování nebo ověření je ovlivněna dvěma hlavními faktory: dobou pulzů, potřebné pro eeprom smazáno, programování a operace čtení a doba posunu, která závisí na frekvenci TCK (testovací hodiny) a počet cyklů potřebných pro přenos pokynů, adres a dat.Protože různá zařízení schopná ISP mají různé počty buněk EEPROM, celkové pevné i variabilní časy jsou pro každé zařízení jedinečné.Celkový čas ISP lze vypočítat jako funkce frekvence TCK, počtu cílových zařízení a architektury EEPROM.

Aplikace EPM7064STC100-7

Vestavěné systémy

EPM7064STC100-7 se široce používá v vestavěných systémových aplikacích, kde slouží jako flexibilní programovatelné logické řešení pro kontrolu různých periferií, zpracování signálů a implementaci vlastních protokolů.Jeho schopnost propojit s mikrokontroléry a senzory umožňuje optimalizovat výkon systému při zachování kompaktní stopy.Díky své vysokorychlostní operaci a nízké spotřebě energie je to vynikající volba pro vestavěné aplikace, které vyžadují spolehlivost a účinnost.

Zpracování digitálního signálu (DSP)

Při zpracování digitálního signálu hraje EPM7064STC100-7 roli při implementaci filtrů, modulace signálu a různých matematických funkcích.Jeho rychlé přepínání a nízké zpoždění šíření je vhodné pro manipulaci s vysokofrekvenčními úkoly zpracování dat, což zajišťuje minimální latenci při přeměně a manipulaci signálu.Běžně se používá při zpracování zvuku, telekomunikacích a radarových systémech.

Datová komunikace

EPM7064STC100-7 se rozsáhle používá v systémech vytváření sítí a datových komunikací kvůli jeho schopnosti zpracovávat logicky náročné operace, jako je směrování dat, vyrovnávání a korekce chyb.Jeho programovatelné I/O schopnosti mu umožňují přizpůsobit se různým komunikačním protokolům, což z něj činí cennou součást v přepínačích, směrovačích a telekomunikační infrastruktuře.Jeho podpora pro programovatelnost in-systému (ISP) také umožňuje aktualizace pole a zlepšuje přizpůsobivost v dynamickém prostředí sítí.

Průmyslová automatizace

Průmyslové aplikace vyžadují vysokou spolehlivost, trvanlivost a nízkou spotřebu energie, díky čemuž je EPM7064STC100-7 preferovanou volbou pro programovatelné logické řadiče (PLC), řízení motorů a automatizované testovací zařízení.Díky své programovatelnosti v systému založené na JTAG poskytuje schopnost zdokonalovat automatizační procesy, aniž by vyžadoval fyzické odstranění nebo přepracování.Díky její všestrannosti kompatibility napětí je také vhodná pro propojení s širokou škálou senzorů a ovladačů používaných v průmyslových prostředích.

Podobné části EPM7064STC100-7

• • EPM7064STC44-10N

• • EPM7064STC100-6

• • EPM7064STC100-10

Výhody EPM7064STC100-7

Programovatelnost systému (ISP)

Jednou z největších výhod EPM7064STC100-7 je jeho schopnost být přeprogramována, zatímco je stále namontována v systému.To eliminuje potřebu odstranění čipu pro aktualizace, zkrácení doby údržby a zlepšení účinnosti.Můžete implementovat úpravy designu bez přerušení výroby, což z něj činí nákladově efektivní řešení pro dlouhodobé projekty.

Vysokorychlostní výkon

Zařízení podporuje vysokou vnitřní provozní frekvenci až 166,7 MHz, což umožňuje rychlé zpracování dat a doby odezvy.Díky tomu je ideální pro aplikace vyžadující zpracování signálu, kontrolu logiky a vysokorychlostní propojení, což zajišťuje hladší a spolehlivější provoz systému.

Všestranná podpora I/O

EPM7064STC100-7 nabízí flexibilitu v návrhu systému a kompatibilita s až 68 konfigurovatelnými I/O kolíky a kompatibilitou s více úrovněmi napětí (3,3V, 5V a tolerantní možnosti pro 2,5 V, 3,3 V a 5V).Umožňuje bezproblémovou integraci do různých obvodů a podporuje prostředí smíšeného napětí a snižuje problémy s kompatibilitou s jinými komponenty.

Spolehlivá operace napříč prostředími

EPM7064STC100-7, navržený tak, aby fungoval v teplotním rozmezí 0 ° C až 70 ° C, zajišťuje konzistentní a stabilní provoz v různých podmínkách.Tato spolehlivost z něj dělá preferovanou volbu pro aplikace, kde je vyžadována stabilita životního prostředí, jako je průmyslová automatizace, telekomunikace a zabudované řídicí systémy.

EPM7064STC100-7 Schéma balíčku

EPM7064STC100-7 je CPLD (komplexní programovatelné logické zařízení) ze série Max 7000s Altera, umístěné ve 100-pinovém tenkém čtyřkolském plochém balíčku (TQFP-100).Tento typ balíčku je navržen pro povrchové aplikace a nabízí rovnováhu s vysokou hustotou pinů a kompaktní velikosti.The diagram pin-out Sleduje schéma číslování proti směru hodinových ručiček, přičemž pin 1 se nachází v levém horním rohu balíčku.Pohybující se proti směru hodinových ručiček, prvních 25 kolíků zabírá levou stranu, kolíky 26 až 50 jsou umístěny podél spodního okraje, kolíky 51 až 75 pokračují podél pravé strany a kolíky 76 až 100 jsou distribuovány podél horního okraje.The Balíček TQFP-100 Má tenké vodiče sahající ven ze všech čtyř stran plochého čtvercového těla.Tento design zvyšuje kompatibilitu povrchu a přitom zachovává odpovídající mezery pro snadné pájení a montáž.Hřeďové hřiště (vzdálenost mezi sousedními kolíky) je obvykle 0,5 mm, optimalizuje integritu signálu a zároveň minimalizuje celkovou stopu.

Výrobce EPM7064STC100-7

EPM7064STC100-7 je CPLD (komplexní programovatelné logické zařízení) původně vyvinuté polovodičovou společností Altera známou pro své programovatelné logické řešení.V roce 2015, Intel získala Alterra a integrovala své produktové řady FPGA a CPLD do skupiny Intel Programmable Solutions Group (PSG).Od té doby byl EPM7064STC100-7 označen pod Intel, ačkoli byl označen jako zastaralý.Společnost Intel, jako výrobce, si udržovala dědickou podporu pro CPLD série Max® 7000S, včetně tohoto modelu, přičemž postupně přesouvala své zaměření na moderní FPGA a programovatelné logické technologie.

Závěr

EPM7064STC100-7 sdružuje komplexní funkce, rychlý výkon a snadné aktualizace v jednom čipu, což dokazuje jeho hodnotu v náročných digitálních nastaveních.Tato příručka ukázala, jak to funguje, na co se používá a jak se hodí do různých elektronických systémů.Pomáhá zajistit, aby zařízení běžela hladce a efektivně, což dokazuje, že je to stále velmi užitečné pro mnoho aplikací.Tato příručka poskytuje jasný pohled na to, jak může EPM7064STC100-7 pomoci efektivně zlepšit elektronické návrhy a systémové operace.

DataSheet PDF

Datové listy EPM7064STC100-7:

O nás

ALLELCO LIMITED

Přečtěte si více

Rychlý dotaz

Zašlete prosím dotaz, budeme odpovědět okamžitě.

Často kladené otázky [FAQ]

1. Jak se zpoždění šíření šíření 7,5ns dopadu EPM7064Stc100-7 Impact Circuit?

Zpoždění šíření 7,5NS zajišťuje zpracování signálu s nízkou latencí, díky čemuž je tento CPLD vhodný pro vysokorychlostní aplikace, jako je zpracování digitálního signálu (DSP), komunikační systémy a průmyslová automatizace, které vyžadují přesné ovládání načasování.

2. Může být EPM7064STC100-7 naprogramován pomocí moderních vývojových nástrojů?

Ano, lze jej naprogramovat pomocí softwaru Intel's Quartus II (dříve Altera Quartus) spolu s vhodným programátorem JTAG.Podpora starších CPLD, jako je EPM7064STC100-7, však může být v novějších kvartusových verzích omezena, takže možná budete muset používat starší verze, jako je Quartus II 13.0 SP1, které stále podporují zařízení řady Max® 7000S.

3. Podporuje prostředí EPM7064STC100-7 prostředí smíšené napětí?

Ano, podporuje logické úrovně 3,3V a 5V, takže je kompatibilní s širokou škálou digitálních obvodů.Tato flexibilita je užitečná pro komponenty pro rozhraní Legacy 5V s moderními 3,3V systémy bez doplňkových měnících obvodů.

4. Jaká je nejlepší metoda pro odstraňování problémů s designem založeným na EPM7064STC100-7?

Chcete -li vyřešit problémy, můžete pro monitorování signálů použít logický analyzátor signálního signálu II nebo externí osciloskopy a logické analyzátory.Pokud ladí problémy s programováním JTAG, ujistěte se, že připojení TDI, TDO, TCK a TMS jsou správné a že používáte kompatibilní bazint USB nebo programátor BYTEBLASTERMV.

5. Mohu naprogramovat EPM7064STC100-7, aniž bych jej odstranil z mé desky obvodu?

Ano.Programovatelnost 5,0V v systému (ISP) prostřednictvím JTAG (IEEE 1149.1) vám umožňuje přeprogramovat zařízení, zatímco zůstává v systému.Díky tomu jsou aktualizace firmwaru, ladění a testování mnohem efektivnější ve srovnání s tradičními CPLD.

Kompletní průvodce odporem 10K: barevný kód, aplikace a obvod

na 2025/03/10

Kondenzátory vs. baterie: Co je nejlepší pro vaše energetické potřeby?

na 2025/03/7

Populární příspěvky

-

Komplexní instrukční sada Počítače: Jak změnily výpočetní techniku?

na 8000/04/18 147760

-

USB-C pinout a funkce

na 2000/04/18 111973

-

Použití primitiv simulace Xilinx Unified: Komplexní průvodce designem a simulací FPGA

na 1600/04/18 111351

-

Napájecí napětí v elektronice: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/18 83741

-

Průvodce konektorem RJ45: Pinout, zapojení, typy kabelů a použití

na 1970/01/1 79527

-

Konečný průvodce barevnými kódy drátu v moderních elektrických systémech

Způsob, jakým naše elektrické systémy používají barvy, není jen pro vzhled.Každá barva drátu nyní označuje specifickou funkci, což usnadňuje správnou identifikaci a zpracování elektrických komponen...na 1970/01/1 66935

-

Průvodce čištění ventilu: funkce, příznaky, testování a náhrada za optimální výkon motoru

Vyčistit ventil je klíčovou součástí systému automobilu, který pomáhá udržovat vzduch čistý správou palivových párů, než mohou uniknout do atmosféry.To nejen pomáhá životnímu prostředí snížením zne...na 1970/01/1 63086

-

Kvalita (Q) Faktor: Rovnice a aplikace

Faktor kvality, neboli „Q“, je důležitý při kontrole toho, jak dobře induktory a rezonátory pracují v elektronických systémech, které používají rádiové frekvence (RF).„Q“ měří, jak dobře obvod mini...na 1970/01/1 63025

-

Dosažení maximálního výkonu s maximální větou přenosu energie

Maximální věta o přenosu výkonu vysvětluje, jak energie ze zdroje, jako je baterie nebo generátor, proudí do připojeného zatížení.Ukazuje přesnou podmínku, kdy zatížení přijímá nejvíce energie.Tent...na 1970/01/1 54092

-

Specifikace a kompatibilita baterie A23

Baterie A23 je malá baterie ve tvaru válce s vysokým napětím.Také se nazývá 23A, 23AE nebo MN21, běží při 12 voltech a mnohem vyšší než AA nebo AAA baterie.Díky jeho speciálnímu designu je...na 1970/01/1 52166