EP2S60F672C4 FPGA: Funkce, aplikace, programování a datový průvodce

V této příručce získáte jasný přehled o EP2S60F672C4, výkonné FPGA z rodiny Stratix II společnosti Intel.Dozvíte se o jeho hlavních funkcích, architektuře, struktuře bloků a technických specifikacích, abyste pochopili, jak se hodí do pokročilých digitálních návrhů.Také vás prochází prostřednictvím svých programovacích kroků, aplikací, výhod a nevýhod, abyste mohli přesně vidět, kde a jak lze toto zařízení použít.Katalog

Co je to EP2S60F672C4?

The EP2S60F672C4 je FPGA s vysokou hustotou od Intel (dříve Altera), která patří do rodiny Stratix II.Postaveno na procesu 90 nm, 1,2 V Copper SRAM, poskytuje podstatnou logickou kapacitu v rámci balíčku FBGA 672-míčků, což je ideální pro komplexní digitální systémy.V rámci série EP2S zařízení „60“ sedí v rozsahu sestavy Stratix II v polovině-upper sestavě a nabízí silnou rovnováhu hustoty logické hustoty, zabudovanou paměť a I/O prostředky.Tato FPGA, známá pro svou robustní architekturu a spolehlivost, zůstává důvěryhodnou volbou v mnoha pokročilých návrzích.

Hledáte EP2S60F672C4?Kontaktujte nás a zkontrolujte aktuální zásoby, dodací lhůtu a ceny.

EP2S60F672C4 CAD modely

EP2S60F672C4 SYMBOL

Footprint EP2S60F672C4

EP2S60F672C4 3D model

Funkce EP2S60F672C4

• • Pokročilý 90 nm, 1,2 V CMOS Proces

EP2S60F672C4 je vyroben na procesu All-vrstvového měděného CMOS 90 nm, který běží při jádrovém napětí 1,2 V.Tato technologie umožňuje vysokou rychlost, sníženou spotřebu energie a větší logickou hustotu ve srovnání se staršími generacemi FPGA.

• • Architektura adaptivního logického modulu (ALM)

Zařízení používá almužnu jako logický stavební blok místo tradičních logických prvků.Tato architektura zlepšuje využití zdrojů a umožňuje účinně implementovat složitější logické funkce ve stejné oblasti křemíku.

• • Vysoká logická hustota

S přibližně 60 440 logickými prvky (24 176 almužny) podporuje FPGA velké a sofistikované digitální vzory.Díky této vysoké kapacitě je vhodná pro aplikace, jako je zpracování signálu, komunikace a vložené řídicí systémy.

• • Paměť Trimatrix ™ na čipu

EP2S60F672C4 integruje tři typy bloků RAM (M512, M4K a M-RAM), aby poskytovaly celkem přibližně 2,4 mbity zabudované paměti.Tato směs umožňuje efektivně implementovat malé FIFOS, střední vyrovnávací paměti a velké vzpomínky s dvojím portem.

• • Vyhrazené bloky DSP

Zařízení obsahuje 36 vyhrazených bloků DSP určených pro aritmetické operace, jako jsou multiplikace, akumulace a filtrování FIR.Tyto bloky zvyšují výkon v úkolech náročných na výpočet a zároveň šetří obecné logické zdroje.

• • Vysokorychlostní integrita I/O a signálu

Podporuje různé jednorázové a diferenciální standardy I/O spolu s obvody dynamického fázového zarovnání (DPA).Tyto funkce umožňují stabilní vysokorychlostní přenos dat do 1 Gbps, což zajišťuje spolehlivou komunikaci s externími komponenty.

• • Podpora bohaté externí paměťové rozhraní

FPGA je kompatibilní s DDR, DDR2, QDR II, RLDRAM II a dalšími paměťovými standardy.Podpora vestavěného rozhraní zjednodušuje návrh desky a dosahuje vysoké propustnosti dat pro aplikace náročné na paměť.

• • Flexibilní správa hodin

Až 12 PLL na čipu umožňuje násobení hodin, dělení, posun fáze a přepínání bez závad.Můžete doladit hodinové domény a snížit chvění a podporovat vnitřní hodinové frekvence až 500–550 MHz.

• • Bitstream šifrování a rekonfigurace

EP2S60F672C4 podporuje šifrování založené na AES pro zajištění duševního vlastnictví.Nabízí také vzdálenou schopnost rekonfigurace a umožňuje aktualizace v terénu bez výměny zařízení.

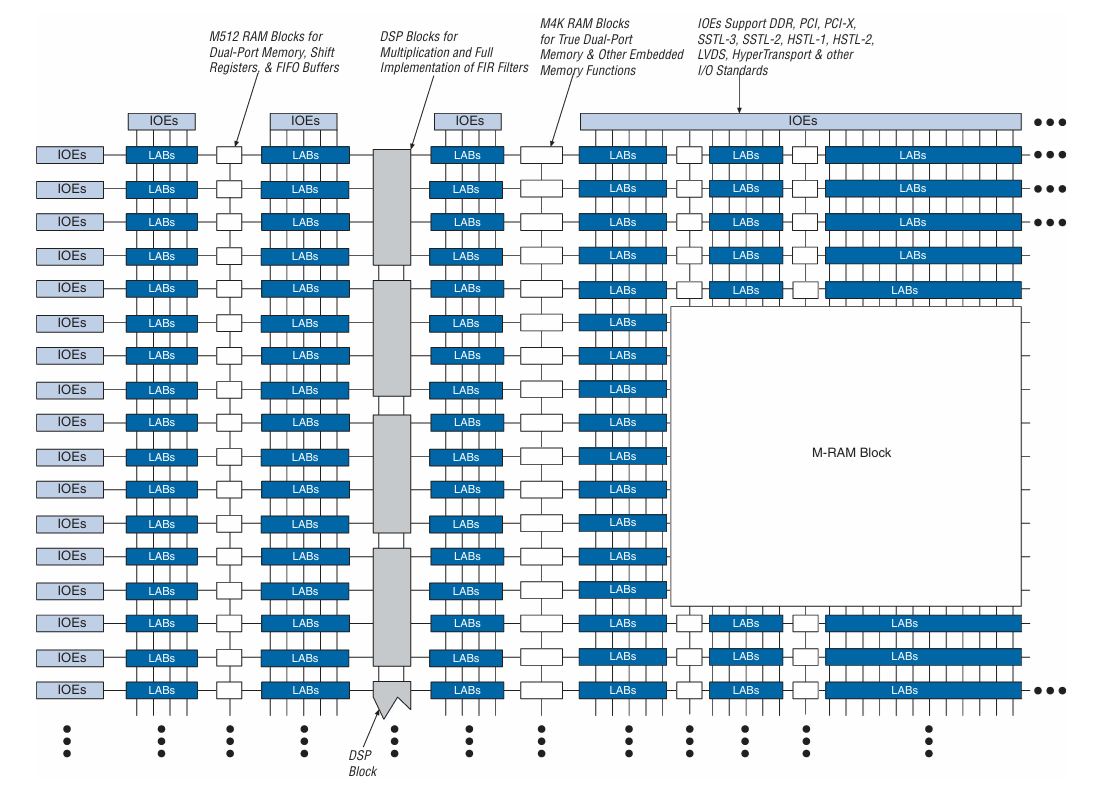

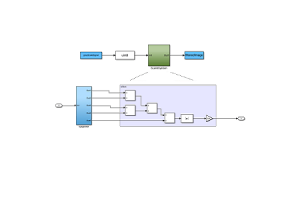

Schéma Stratix II

Blokový diagram STRATIX II, jak je znázorněno pro EP2S60F672C4, ilustruje interní uspořádání logických, paměťových a DSP zdrojů, které tvoří jádro FPGA.Logické pole pole (LABS) jsou uspořádány v běžné mřížce obklopené vloženými sloupci RAM a DSP, které poskytují rychlé aritmetické a na čipové úložné schopnosti.Periferní I/O prvky a hodinové sítě rámují tuto strukturu a umožňují efektivní přenos dat a ovládání načasování mezi FPGA a externími zařízeními.Tento diagram je důležitý, protože pomáhá pochopit, jak jsou různé funkční bloky fyzicky organizovány, což jim umožňuje optimalizovat umístění, směrování a celkový výkon systému.

Schéma bank Stratix II/O Banks

Tento diagram Banks Stratix II/O ilustruje, jak jsou seskupeny vstupní/výstupní kolíky EP2S60F672C4 a jaké elektrické standardy podporuje každá skupina.Každá banka I/O je navržena tak, aby zpracovávala specifické úrovně napětí, typy signalizace a funkce, jako jsou vstupní standardy LVTTL, SSTL, LVDS nebo hodiny.Rozložení ukazuje, jak jsou různé banky (např. 1, 2, 5, 6 vs. 3, 4, 7, 8 atd.) Optimalizovány buď pro obecné I/O nebo vysokorychlostní diferenciální signalizaci, včetně podpory pro vstupy hodin LVD/LVPECL na okrajích.Pochopení této struktury je důležité při přiřazování kolíků, protože správný výběr banky zajišťuje elektrickou kompatibilitu, zjednodušuje směrování desky a maximalizuje výkon FPGA ve vysokorychlostních návrzích.

Specifikace EP2S60F672C4

|

Typ |

Parametr |

|

Výrobce |

Altera/intel |

|

Série |

STRATIX® II |

|

Obal |

Podnos |

|

Stav dílu |

Zastaralý |

|

Počet laboratoří/CLB |

3022 |

|

Počet logických prvků/buněk |

60 440 |

|

Celkové bity RAM |

2 544 192 |

|

Počet I/O. |

492 |

|

Napětí - napájení |

1,15 V ~ 1,25 V |

|

Typ montáže |

Povrchová držák |

|

Provozní teplota |

0 ° C ~ 85 ° C (TJ) |

|

Balíček / pouzdro |

672-BBGA |

|

Balíček dodavatelského zařízení |

672-FBGA (27 × 27) |

|

Číslo základního produktu |

EP2S60 |

Aplikace EP2S60F672C4

1. Zpracování digitálního signálu (DSP) a filtrování

EP2S60F672C4 je vhodný pro implementaci vysoce výkonných funkcí DSP, jako jsou FIR a IIR filtry, zpracování FFT a komplexní aritmetické operace.Jeho vyhrazené bloky DSP zpracovávají efektivně multiplikace a akumulace a uvolňují obecné logické zdroje pro další úkoly.Paměť On-Chip Trimatrix ™ umožňuje hladké datům a potrubí, což je skvělé pro zpracování v reálném čase při vysokých vzorkovacích frekvencích.Díky tomu je zařízení ideální pro pokročilé zvukové, video a radarové signálové aplikace.

2. vysokorychlostní komunikace a vytváření sítí

Vysokorychlostní I/O rozhraní I/O FPGA a dynamické fázové zarovnání (DPA) obvody podporují spolehlivé přenos dat na úrovni gigabitu.Může implementovat komunikační protokoly a funkce fyzikální vrstvy pro systémy, jako jsou směrovače, přepínače a propojení zadního rovinky.Díky své velké logické kapacitě a flexibilním PLL může spravovat složité načasování a konverze protokolu mezi více vysokorychlostními rozhraními.Díky těmto schopnostem je silně vhodná pro telekomunikační infrastrukturu a síťové zařízení s vysokou šířkou šířky šířky.

3. řadiče paměti a systémy zpracování dat

EP2S60F672C4 podporuje různá externí rozhraní paměti včetně DDR, DDR2, RLDRAM II a QDR II, což je ideální pro navrhování řadičů paměti s vysokou šířkou.Dokáže zpracovávat vyrovnávání dat, generování adresy a rozhodčí řízení při vysokých rychlostech s minimální latencí.Kombinace rychlých hodinových sítí a zabudovaných bloků RAM umožňuje efektivní správu velkých datových toků.Díky tomu je FPGA vhodná pro zpracování obrazu, streamování videa a vědecké výpočetní platformy, které se spoléhají na propustnost těžkých dat.

4. Vlastní logika a zabudované zrychlení

S více než 60 000 logickými prvky a bohatým správou hodin může FPGA hostit přizpůsobené hardwarové akcelerátory pro konkrétní algoritmy.Návrháři jej často používají k vykládání výpočetně intenzivních úkolů z CPU, jako je šifrování, analýzu protokolu nebo kontrolní smyčky v reálném čase.Může také integrovat více funkčních bloků, takže je vhodný pro složité vzory podobné SOC.Díky této flexibilitě je cenná v aplikacích, jako jsou průmyslové automatizace, bezpečnostní systémy a kontrolní jednotky letectví.

5. platformy prototypování a vývoje vzdělávání

Zařízení EP2S60 se běžně vyskytuje na vývojových soupravách FPGA používané pro prototypování, testování a akademický výzkum.Jeho rovnováha logické kapacity, počtu I/O a schopnosti DSP umožňují inženýrům a studentům implementovat a ověřit úplné systémy na jednom čipu.Podporuje rychlou iteraci digitálních návrhů, což umožňuje ověření hardwaru před zavázáním k rozvoji ASIC.Mnoho univerzit a výzkumných a vývojových laboratoří to používá k výuce pokročilých konceptů digitálního designu a zpracování signálů.

EP2S60F672C4 Podobné části

|

Specifikace |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Rodina / série |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

Logické prvky (LE) |

60 440 |

60 440 |

60 440 |

60 440 |

60 440 |

60 440 |

|

Almužna |

24 176 |

24 176 |

24 176 |

24 176 |

24 176 |

24 176 |

|

Balík |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Rychlostní stupeň |

C4 (STD) |

C3 (rychlejší) |

C5 (rychlejší) |

C5 (rychlejší) |

I4 (STD) |

I3 (rychlejší) |

|

Teplotní stupeň |

Komerční (0 ~ 70 ° C) |

Komerční |

Komerční |

Komerční |

Průmyslová (−40 ~ 100 ° C) |

Průmyslová (−40 ~ 100 ° C) |

|

I/O kolíky |

492 |

492 |

492 |

492 |

492 |

492 |

|

Paměť na čipu |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

|

Napětí jádra |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

1,2 v |

|

Rozdíl klíčů |

Základní komerční rychlost |

C3 rychlostní koš, bez olova „n“ |

Vyšší rychlostní koš |

Varianta „n“ s vyšší rychlostí, varianta „n“ |

Průmyslová teplota, stejná hustota |

Průmyslová, rychlejší rychlost, bez olova |

Kroky programování EP2S60F672C4

Než budete moci použít EP2S60F672C4 FPGA ve svém návrhu, musíte jej správně nakonfigurovat pomocí kompilovaného bitstream.Tento proces zahrnuje přípravu programovacího souboru, nastavení hardwarového rozhraní a zajištění toho, aby se konfigurace správně načítala na zapnutí.

Krok 1: Vytvořte a kompilujte svůj design

Začnete vývojem logického designu pomocí softwaru Intel Quartus II.Po dokončení návrhu jej zkompilujete a vygenerujete programovací soubor (.SOF nebo .POF) speciálně pro zařízení EP2S60F672C4.Proces kompilace kontroluje načasování, přiřazení PIN a využití zdrojů, aby se zajistilo, že váš design zapadá do architektury FPGA.Jakmile je kompilován, váš BitStream je připraven na konfiguraci zařízení.

Krok 2: Nastavte programovací hardware

Dále připravíte rozhraní fyzického programování mezi počítačem a deskou FPGA.Obvykle to zahrnuje připojení kabelu USB-Blaster nebo kompatibilního JTAG k portu JTAG zařízení.Měli byste ověřit, že Quartus II rozpozná programátor a že cílové zařízení je správně detekováno.Tento krok zajišťuje stabilní komunikaci před zahájením procesu konfigurace.

Krok 3: Načíst programovací soubor do zařízení

Pomocí nástroje pro programátoru Quartus II přidáte kompilovaný soubor .SOF nebo .POF a ze seznamu detekovaných zařízení vyberte EP2S60F672C4.Poté zahájíte programovací sekvenci, během níž je BitStream přenesen a načten do konfiguračních buněk SRAM FPGA.Měli byste monitorovat lištu pokroku a stavové zprávy, abyste potvrdili úspěšnou konfiguraci.Po dokončení začíná FPGA okamžitě provádět programovanou logiku.

Krok 4: Ověřte konfiguraci a provoz

Po programování ověřte, že zařízení funguje tak, jak bylo zamýšleno.Quartus II poskytuje možnost ověření pro kontrolu konfigurace CRC a stavových signálů a zajišťuje správné načtení návrhu.Můžete také otestovat své I/O funkce nebo spustit funkční simulaci, abyste potvrdili chování systému.Tento poslední krok zajišťuje, že váš design je plně funkční a stabilní na hardwaru.

Výhody a nevýhody EP2S60F672C4

Výhody

• Vysoká logická hustota pro komplexní návrhy

• Dobrý poměr výkonnosti k nákladům

• Snadná migrace ve stejné rodině

• Stabilní a zralé nástroje pro vývoj

• Prokázaná spolehlivost v průmyslovém využití

Nevýhody

• Zastaralé a těžší zdroje

• Vyšší spotřeba energie než novější FPGA

• Žádné moderní vysokorychlostní transceivery

• Obtěžovanější uzavření načasování při vysokém využití

• Omezená škálovatelnost pro budoucí protokoly

Rozměry balení EP2S60F672C4

|

Typ |

Parametr |

|

Typ balíčku |

672-FBGA (Fineline BGA) |

|

Velikost těla (L × W) |

27,00 mm × 27,00 mm |

|

Celková výška balíčku (a) |

Max 3,50 mm |

|

Výška standoff (A1) |

Min 0,30 mm |

|

Tloušťka substrátu (A2) |

Max 3,00 mm |

|

Průměr míče (B) |

0,50 mm - 0,70 mm |

|

Pitch míče (E) |

1,00 mm |

|

Počet koulí |

672 |

|

Styl montáže |

Povrchová držák |

|

Popis balíčku |

FBGA, 27 × 27 mm mřížka |

Výrobce EP2S60F672C4

EP2S60F672C4 FPGA je vyroben pomocí Altera Corporation, přední průkopník v programovatelných logických zařízeních.V roce 2015 byla Altera získána společností Intel, a produkt nyní spadá do skupiny Intel Programmable Solutions Group (PSG), která nadále podporuje a dodává zavedené rodiny FPGA Altera.Intel udržuje linku Stratix II v rámci svého portfolia starších produktů a zajišťuje dokumentaci, podporu nástrojů a dlouhodobou dostupnost pro průmyslové a komunikační aplikace.

Závěr

EP2S60F672C4 kombinuje vysokou logickou hustotu, flexibilní architekturu paměti a robustní I/O funkce pro podporu komplexních digitálních systémů.Jeho design založený na ALM, Trimatrix ™ paměti, bloky DSP a funkce správy hodin umožňují efektivní implementaci náročných aplikací.I když nabízí prokázanou spolehlivost a podporu vývoje zralého, čelí omezením, jako je zastarávání a nedostatek moderních transceiverů ve srovnání s novějšími generacemi FPGA.Celkově je jeho vyvážený výkon a všestrannost z něj solidní volba pro zpracování signálu, komunikaci, zpracování dat a prototypování.

DataSheet PDF

Datové listy EP2S60F672C4:

O nás

ALLELCO LIMITED

Přečtěte si více

Rychlý dotaz

Zašlete prosím dotaz, budeme odpovědět okamžitě.

Často kladené otázky [FAQ]

1. Může EP2S60F672C4 pracovat s moderními rozhraními paměti DDR?

Ano, podporuje rozhraní DDR, DDR2, QDR II a RLDRAM II, která pokrývají mnoho běžných externích paměťových standardů.Díky tomu je vhodný pro aplikace pro zpracování dat s vysokou šířkou šířky.

2. Vyžaduje EP2S60F672C4 speciální zpracování nebo úložiště?

Ano, stejně jako jiné komponenty s balením BGA, měly by být uloženy v balení s ovládáním vlhkosti a manipulovány s ochranou ESD.Dodržování správných postupů skladování pomáhá udržovat pájetelnost a spolehlivost zařízení během montáže.

3. Jak můžete snížit spotřebu energie v návrzích EP2S60F672C4?

Pokud je to možné, můžete optimalizovat logické využití, nevyužité hodiny, nižší napětí I/O, a využít možnosti syntézy výkonu v Quartus II, abyste minimalizovali celkový tah napájení.

4. jaké programovací nástroje jsou vyžadovány pro EP2S60F672C4?

Pro konfiguraci zařízení budete potřebovat software Intel Quartus II pro návrh, kompilaci a programování, spolu s kabelem USB-Blaster nebo kompatibilním kabelem JTAG.

5. Podporuje EP2S60F672C4 aktualizace v terénu nebo vzdálenou rekonfiguraci?

Ano, podporuje šifrování BitStream založené na AES a vzdálenou rekonfiguraci, což vám umožňuje bezpečně aktualizovat systém, aniž by fyzicky nahradil FPGA.

Vše o LFXP6C-3FN256C LATTICE SEMICODUCTOR

na 2025/10/6

XC2C256-7TQ144C CPLD: PINOUT, FUNKCE, Programování a průvodce datovým listem

na 2025/10/3

Populární příspěvky

-

Komplexní instrukční sada Počítače: Jak změnily výpočetní techniku?

na 8000/04/17 147710

-

USB-C pinout a funkce

na 2000/04/17 111648

-

Použití primitiv simulace Xilinx Unified: Komplexní průvodce designem a simulací FPGA

na 1600/04/17 111313

-

Napájecí napětí v elektronice: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/17 83573

-

Průvodce konektorem RJ45: Pinout, zapojení, typy kabelů a použití

na 1970/01/1 79209

-

Konečný průvodce barevnými kódy drátu v moderních elektrických systémech

Způsob, jakým naše elektrické systémy používají barvy, není jen pro vzhled.Každá barva drátu nyní označuje specifickou funkci, což usnadňuje správnou identifikaci a zpracování elektrických komponen...na 1970/01/1 66738

-

Kvalita (Q) Faktor: Rovnice a aplikace

Faktor kvality, neboli „Q“, je důležitý při kontrole toho, jak dobře induktory a rezonátory pracují v elektronických systémech, které používají rádiové frekvence (RF).„Q“ měří, jak dobře obvod mini...na 1970/01/1 62923

-

Průvodce čištění ventilu: funkce, příznaky, testování a náhrada za optimální výkon motoru

Vyčistit ventil je klíčovou součástí systému automobilu, který pomáhá udržovat vzduch čistý správou palivových párů, než mohou uniknout do atmosféry.To nejen pomáhá životnímu prostředí snížením zne...na 1970/01/1 62785

-

Dosažení maximálního výkonu s maximální větou přenosu energie

Maximální věta o přenosu výkonu vysvětluje, jak energie ze zdroje, jako je baterie nebo generátor, proudí do připojeného zatížení.Ukazuje přesnou podmínku, kdy zatížení přijímá nejvíce energie.Tent...na 1970/01/1 54019

-

Specifikace a kompatibilita baterie A23

Baterie A23 je malá baterie ve tvaru válce s vysokým napětím.Také se nazývá 23A, 23AE nebo MN21, běží při 12 voltech a mnohem vyšší než AA nebo AAA baterie.Díky jeho speciálnímu designu je...na 1970/01/1 51932