Komplexní průvodce testovacími zařízeními: Nástroje a techniky pro ověření digitálního systému

Tato příručka zkoumá testbenches, klíčový nástroj pro validaci softwaru, který simuluje podmínky pro testování vstupů a ověření výstupů.TestBenches hrají roli při identifikaci chyb na začátku vývoje a zlepšují spolehlivost softwaru.S praktickými příklady a poznatky tento článek zdůrazňuje jejich použití, techniky a význam při budování silných a efektivních digitálních systémů.Katalog

Role testovacíchbenchů při ověření digitálního systému

TestBench je součástí procesu validace digitálního systému.Nejedná se pouze o nástroj pro generování vstupů a ověřování výstupů, slouží jako komplexní rámec, který simuluje podmínky k posouzení spolehlivosti, funkčnosti a chování digitálních systémů dříve, než budou nasazeni v terénu.Vytvořením kontrolovaných prostředí pro stresové testovací systémy s širokou škálou vstupních scénářů vám testbenches pomůže identifikovat potenciální konstrukční nedostatky na začátku vývojového životního cyklu, dlouho předtím, než je systém vložen do výroby.Tato včasná detekce chyb a zranitelnosti je nutná pro snížení nákladných chyb, zajištění souladu se specifikacemi výkonu a zlepšení celkové spolehlivosti systému.

Kromě ověření správnosti reakcí systému hrají testovací závody roli při hodnocení hranových případů, problémů s načasováním a mechanismům zpracování chyb, což zajišťuje, že systém může správně fungovat i za extrémních nebo neočekávaných podmínek.Prostřednictvím automatizovaného testování a simulace přispívají testovací závody k vyšší kvalitě softwaru, zlepšení výkonu a kratších vývojových cyklů umožněním iteračního testování bez manuálního zásahu.Slouží jako záruka proti selhání, ke kterým by mohlo dojít po nasazení, což zajišťuje robustnost a spolehlivost digitálních systémů.

Klíčové komponenty testovacíhobenchu a jejich funkcí

Abychom lépe porozuměli tomu, jak fungují testování, je důležité prozkoumat komponenty, díky nimž jsou efektivní.Dobře vytvořený testovací zařízení pracuje správou dvou základních úkolů: generování vstupů (podnětů) a ověření výstupů.Pojďme podrobně prozkoumat každou složku.

Generování stimulu

Generování stimulu zahrnuje vytvoření sady vstupních signálů, které simulují podmínky pro testování chování digitálního systému.Tyto vstupy musí být jak přesné, tak realistické, aby se zajistilo, že systém je vystaven různým scénářům, s nimiž se v praxi může setkat.Jako příklad zvažte základní modul RAM.TestBench musí dodávat konkrétní vstupy do modulu a pozorovat jeho výstupy, aby se zajistilo, že se chová podle očekávání.Klíčové vstupy pro modul RAM obvykle zahrnují:

• CLK (hodiny): Řídí načasování systému.

• AdDR (adresa): Určuje, která umístění dat pro přístup.

• Wen (zápis povolit): Řídí, zda jsou data zapsána do paměti.

• Data: Skutečné informace zapsané do modulu.

Výstup, známý jako dataOut, představuje výsledek interních operací modulu.Pečlivým skriptováním toho, jak jsou tyto vstupy dodávány a monitorovali dataOut, můžete ověřit, že systém funguje správně podle různých scénářů.Přemýšlejte o generování stimulu jako nastavení testovacího scénáře v laboratoři.Stejně jako vědci pečlivě kontrolují podmínky, aby pozorovali chemické reakce, digitální designéři vyrábějí přesné vstupy, aby pozorovali, jak systém reaguje.

Ověření výstupu

Výstupní ověření je proces kontroly, že skutečné výstupy systému odpovídají očekávaným výsledkům.Tento krok je rozhodující při chytání chyb brzy předtím, než se vyvinou do větších problémů.Jiní používají ověření výstupu k potvrzení, že systém splňuje zamýšlenou funkčnost a provádí důsledně za různých podmínek.Ověření výstupu zahrnuje automatizované i ruční kontroly.Například:

• Automatizované ověřovací nástroje: Nástroje, jako jsou ModelIm a Quartus, umožňují automatizované testování, kde jsou výstupy systému porovnány s očekávanými výsledky.Tím se zrychluje proces ověření a snižuje chybu.

• Manuální ověření (volitelné): Pro složitější scénáře mohou být nezbytné manuální kontroly, aby se zajistilo, že jsou pokryty konkrétní případy okraje.

Nástroje a techniky pro implementaci testbench

Kvartus: Simulace vizuálního vstupu/výstupu

Quartus poskytuje grafické rozhraní, které vizuálně uspořádá vstupy a pozoruje výstupy.Tato metoda může být prospěšná pro začátečníky nebo pro systémy, které vyžadují více praktický, vizuální přístup.Tím, že Quartus umožňuje interagovat se simulací prostřednictvím grafického prostředí, pomáhá demystifikovat vztah mezi vstupy a výstupy, což usnadňuje pochopení toho, jak se digitální systém chová v čase.Jednou z klíčových silných stránek kvartu je to, že je ideální pro začátečníky.Jeho intuitivní, vizuální rozhraní poskytuje přímý způsob, jak vidět, jak vstupy ovlivňují výstupy bez nutnosti rozsáhlého skriptování nebo znalostí o programování.Zpětná vazba, kterou nabízí, pomáhá snadněji uchopit chování obvodů, což z ní činí užitečný nástroj pro nové design digitálního systému.Quartus však má svá omezení.Nastavení simulací v kvartu může být časově náročné, zejména pro složitější návrhy.Tento nástroj je méně flexibilní ve srovnání s simulačními nástroji založenými na skriptování, které mohou nabídnout více možností přizpůsobení a automatizace.Pro práci na rozsáhlých nebo vysoce detailních systémech může tento nedostatek flexibility představovat výzvu.

ModelIm: Simulace založená na textu pomocí skriptování

ModelIm zaujímá odlišný přístup ke simulaci upřednostňováním vstupu založeného na textu prostřednictvím skriptování.Vytvářejte testovací scénáře pomocí skriptů Verilog (.V) nebo VHDL (.VHD), spíše než vizuálně uspořádat vstupy a výstupy.Tato metoda poskytuje přesnost a kontrolu.Místo spoléhání se na grafické rozhraní definujete, jak by měl být systém testován pomocí podrobných skriptů, což umožňuje větší přizpůsobení a automatizaci v simulačním procesu.Jednou z klíčových silných stránek ModelIM je flexibilita, kterou nabízí.Pomocí skriptů máte větší kontrolu nad testovacími scénáři, což jim umožňuje vytvářet složité a přesné simulace.Jakmile je návrhář obeznámen se syntaxí a pracovním postupem, může být nastavení simulací mnohem rychlejší ve srovnání s používáním grafických nástrojů, jako je Quartus.Schopnost opětovného použití a úpravy skriptů také zvyšuje její účinnost, zejména ve větších projektech.Textový přístup k ModelIm však přichází s určitými omezeními.Vyžaduje solidní porozumění Syntaxi Verilog nebo VHDL, která může představovat výzvu pro začátečníky, kteří nejsou obeznámeni s jazyky popisu hardwaru.Výsledkem je, že ModelIM má ve srovnání s více vizuálními simulačními nástroji strmější křivku učení.Novým uživatelům může být obtížné začít, ale s praxí se přesnost a flexibilita nabízená skriptováním může stát cenným přínosem.

Přemostění teorie a praxe při ověření

TestBenches slouží jako most mezi teoretickými návrhy a aplikacemi tím, že simuluje, jak se digitální systém bude chovat za různých podmínek, včetně případů okrajů a neočekávaných vstupů.V digitálním designu je často obtížné předvídat, jak bude systém fungovat v praxi založené pouze na teoretických modelech.TestBenches uzavírá tuto mezeru tím, že vám umožní přesunout se nad koncepty abstraktního designu a vyhodnotit chování systému v kontrolovaném simulovaném prostředí.Jednou z klíčových výhod používání simulačních nástrojů v testovacíchbencích je okamžitá zpětná vazba, kterou poskytují během ladění.Nástroje jako Multisim nebo Modelsim nabízejí vizuální reprezentace chování systému, ukazující, jak změny ve vstupních vstupech ovlivňují výstupy v průběhu času.Tato zpětná vazba vám umožňuje určit problémy rychleji, sledovat chyby zpět k jejich kořenové příčině a podle toho upravit jejich návrhy.Pokud například systém nesplňuje omezení načasování nebo vykazuje neočekávané chování v určitých vstupních sekvencích, může testovací zařízení tyto nedostatky okamžitě zdůraznit, dlouho předtím, než je systém fyzicky postaven.Identifikací problémů na začátku návrhového cyklu snižují testovací závody potřebu nákladného přepracování a fyzického prototypu, což zefektivňuje proces ověření.Tato validace v rané fázi pomáhá zajistit, aby digitální systémy byly jak funkčně správné, tak odolné vůči podmínkám, což z nich činí spolehlivější a snižuje riziko selhání po nasazení.Tímto způsobem testbenches působí jako praktický nástroj pro transformaci teoretických návrhů na robustní.

Pokročilá architektura testbench

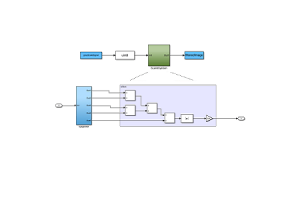

Pokročilé testovací zařízení přesahují jednoduché testování vstup-výstup začleněním dalších komponent pro správu komplexních systémů.Standardní testovací zařízení zahrnuje tři klíčové části: Stimulační generátor K vytvoření vstupních signálů a Testovací design (DUT), což je skutečný testovaný hardware a Výstupní monitor to kontroluje výstupy proti očekávaným výsledkům.Tyto komponenty spolupracují na zajištění důkladnějšího a přesnějšího ověření digitálních návrhů.

Zlepšení přesnosti TestBench zahrnuje použití technik, které zajišťují, že design působí spolehlivě v různých scénářích. Randomizované testování Představuje nepředvídatelné vstupní vzorce pro ověření stability systému za různých podmínek. Testování případů Zaměřuje se na hraniční situace, kdy se systém s největší pravděpodobností setká s chybami.A konečně, Regresní testování Zahrnuje opětovné běh testů po změnách, aby se potvrdilo, že nebyly zavedeny žádné nové problémy, což zajišťuje, že systém zůstává v průběhu času konzistentní a bezchybný.

Skriptační testovací zařízení

Chcete -li vytvořit efektivní a spolehlivé testovací závody ve Verilogu nebo VHDL, sledujte klíčové osvědčené postupy.Spusťte jednoduché a poté nejprve rozšířte testováním základní funkce a postupně přidáním složitějších scénářů.Použijte komentáře a dokumentaci, abyste své skripty usnadnili pochopení a údržbu jasným vysvětlením každé sekce.Nakonec, pokud je to možné, automatizujte, abyste ušetřili čas a zmenšili chyby pomocí smyček a funkcí pro zpracování opakujících se úkolů a vstupních vzorců.

O nás

ALLELCO LIMITED

Přečtěte si více

Rychlý dotaz

Zašlete prosím dotaz, budeme odpovědět okamžitě.

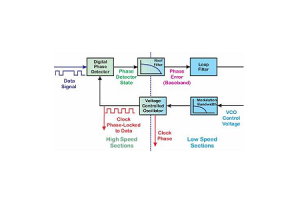

Digitální fázová smyčka (DPLL): Návrh, komponenty a operace

na 2025/01/7

Evoluce a dopad architektury RISC v moderním výpočtu

na 2025/01/7

Populární příspěvky

-

Komplexní instrukční sada Počítače: Jak změnily výpočetní techniku?

na 8000/04/18 147760

-

USB-C pinout a funkce

na 2000/04/18 111969

-

Použití primitiv simulace Xilinx Unified: Komplexní průvodce designem a simulací FPGA

na 1600/04/18 111351

-

Napájecí napětí v elektronice: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/18 83733

-

Průvodce konektorem RJ45: Pinout, zapojení, typy kabelů a použití

na 1970/01/1 79522

-

Konečný průvodce barevnými kódy drátu v moderních elektrických systémech

Způsob, jakým naše elektrické systémy používají barvy, není jen pro vzhled.Každá barva drátu nyní označuje specifickou funkci, což usnadňuje správnou identifikaci a zpracování elektrických komponen...na 1970/01/1 66930

-

Průvodce čištění ventilu: funkce, příznaky, testování a náhrada za optimální výkon motoru

Vyčistit ventil je klíčovou součástí systému automobilu, který pomáhá udržovat vzduch čistý správou palivových párů, než mohou uniknout do atmosféry.To nejen pomáhá životnímu prostředí snížením zne...na 1970/01/1 63082

-

Kvalita (Q) Faktor: Rovnice a aplikace

Faktor kvality, neboli „Q“, je důležitý při kontrole toho, jak dobře induktory a rezonátory pracují v elektronických systémech, které používají rádiové frekvence (RF).„Q“ měří, jak dobře obvod mini...na 1970/01/1 63024

-

Dosažení maximálního výkonu s maximální větou přenosu energie

Maximální věta o přenosu výkonu vysvětluje, jak energie ze zdroje, jako je baterie nebo generátor, proudí do připojeného zatížení.Ukazuje přesnou podmínku, kdy zatížení přijímá nejvíce energie.Tent...na 1970/01/1 54090

-

Specifikace a kompatibilita baterie A23

Baterie A23 je malá baterie ve tvaru válce s vysokým napětím.Také se nazývá 23A, 23AE nebo MN21, běží při 12 voltech a mnohem vyšší než AA nebo AAA baterie.Díky jeho speciálnímu designu je...na 1970/01/1 52163