Vysvětleno CPLD: Průvodce programovatelnými logickými zařízeními

V dynamickém světě elektronického designu vynikají komplexní programovatelná logická zařízení (CPLD) jako všestranné nástroje, hladce mísí přizpůsobivost, přesnost a účinnost.Tato zařízení revolucionizovala návrh obvodu zavedením programovatelných makro buněk a dominantní propojovací matice, což umožňuje vytvoření složitých logických funkcí s pozoruhodnou spolehlivostí.Od jejich založení v 80. letech až po jejich klíčovou roli v moderních průmyslových odvětvích, jako je síťová, automobilový průmysl a letecký průmysl, se pro vás CPLDS ukázalo jako hledat flexibilitu i výkon.Tento článek se vrhá na cestu CPLDS, jejich výrazných rysů, praktických aplikací a metodik programování, které z nich činí základní kámen v designu digitální logiky.Katalog

Přehled CPLD

V rámci nadvlády komplexních programovatelných logických zařízení (CPLDS) objevuje jeden sofistikovaný gobelín programovatelných logických makro buněk, propletených dominantní propojovací maticí.Tyto linky jednotky vstupu/výstupu (I/O) vstupů (MC) a vstupní/výstupy (I/O) umožňují obratně navrhovat obvody a konfigurovat struktury pro jedinečné funkce.Na rozdíl od zařízení, která jsou zmatena jejich složitým načasováním propojení, CPLD používají nemovité kovové dráty.Tato charakteristika jim dává konzistentní a předvídatelné chování hodin, díky čemuž jsou předpovědi načasování spolehlivější a přesnější.

Cesta a využití

Sedmdesátá léta ohlašovala příchod programovatelných logických zařízení (PLDS) a podpořila přechod směrem k programovatelným makro jednotkám.Tento posun zavedl dostatečnou flexibilitu designu a odlišuje je od statických digitálních obvodů, ačkoli jejich užitečnost byla zpočátku omezena na jednodušší obvody.Příchod CPLDS v polovině 80. let revolucionizoval tuto krajinu a připravoval cestu pro složité návrhy obvodů.Od té doby se tkali do struktury průmyslových odvětví, jako je síťová, automobilová elektronika, obrábění CNC a letecké systémy.Můžete si vzpomenout na způsob, jakým CPLDS zjednodušené procesy, které kdysi vyžadovaly pečlivou manuální práci, což znamenalo pozoruhodný skok v účinnosti.

Výrazné vlastnosti CPLD

CPLD se rozlišují prostřednictvím svého přizpůsobivého programování, rozsáhlé integrace, rychlých vývojových schopností a rozsáhlé použitelnosti spolu s ekonomickými výrobními náklady.Přitahují se na ty, kteří mají minimální hardwarový zážitek, slouží jako spolehlivé a zabezpečené produkty, které nevyžadují vyčerpávající testování.Jako důkaz jejich statečnosti ve velkých návrzích obvodů hrají CPLD klíčovou roli při vývoji prototypů a podávají běhy pod 10 000 jednotek, což pro vás ztělesňuje užitečnou kompetence.Adepty, s jakou se CPLD přizpůsobují vyvíjejícím se požadavkům projektu, jim často získává uznání a zdůrazňuje jejich skutečnou všestrannost v dynamickém prostředí.

Metody aplikací

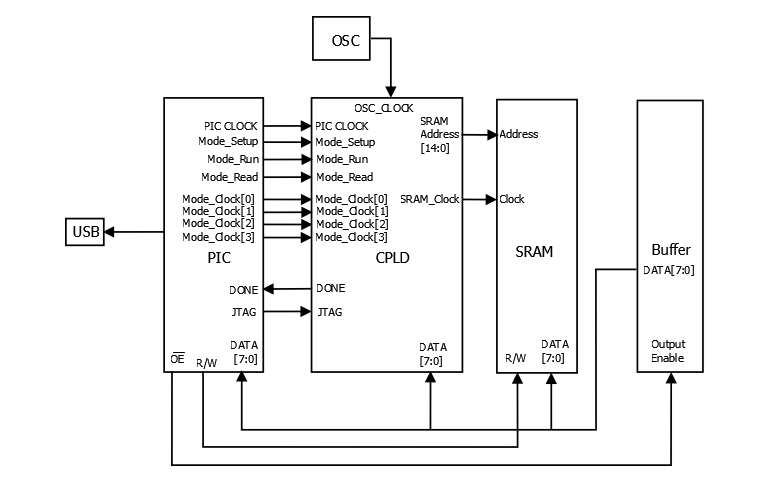

Tyto integrované obvody vám umožňují rozpracovat logické funkce přizpůsobené jejich potřebám pomocí jazyků popisu schémat i hardwaru na vývojových platformách.Například při navrhování záznamníku se na počítači připravují a kompilovány a kompilované popisy hardwaru.S využitím kabelu stahování je kód přenesen do CPLD pro programování v systému, které zahrnuje testování, odstraňování problémů a vylepšení návrhů.Úspěšně vytvořené vzory jsou pak hromadně vyráběny replikací čipů CPLD.V projektech, jako jsou systémy semaforů, se opakování procesu navrhování stane nezbytným, podobně jako přestavba domu k obnovení jeho novosti.Tato opakující se metodologie často stanoví základy pro zvládnutí, zvyšování dovedností i důvěry.

Vedoucí varianty

V průběhu let odhalily společnosti jako Altera, Lattice a Xilinx prominentní řady CPLDS.Mezi pozoruhodné příklady patří Altera EPM7128S, Mříže LC4128V, a Xilinx's XC95108 .Tyto modely našly významné role napříč různými globálními aplikacemi.Ti, kteří měli tu čest pracovat s těmito odlišnými produkty, často uvádějí jemné, ale silné rozdíly, které optimalizují konkrétní funkce.To odráží proces jemného výběru ovlivněný specifickými požadavky projektu, kde každá varianta drží svou jedinečnou přitažlivost.

Identifikace a klasifikace FPGA a CPLD

|

Aspekt |

Cpld |

FPGA |

|

Tvorba logického chování |

Vytváří logické chování pomocí struktury termínu produktu.

Příklady: Série Lattice ISPLSI, řada Xilinx XC9500, Altera Max7000s

Série, Lattice Mach Series |

Formují logické chování pomocí metody vyhledávání tabulky.

Příklady: řada Xilinx Spartan, Altera Flex10K, ACEX1K Série |

|

Vhodnost |

Vhodné pro algoritmy a kombinační logika, Works

Lepší s omezenými spouštěmi a bohatými produktovými podmínkami |

Vhodné pro sekvenční logiku, funguje lépe s

struktury bohaté na spouštěče |

|

Zpoždění načasování |

Struktura kontinuálního zapojení poskytuje uniformu a

předvídatelné zpoždění načasování |

Segmentovaná struktura zapojení vede k nepředvídatelnému načasování

zpoždění |

|

Flexibilita programování |

Opravené vnitřní obvody jsou upraveny pro programování.

Používá se programování na úrovni logického bloku |

Interní zapojení je upraveno pro programování.Logika

Programování na úrovni brány umožňuje větší flexibilitu |

|

Integrace |

Nižší integrace ve srovnání s FPGA |

Vyšší integrace se složitější strukturou zapojení a

Logická implementace |

|

Snadné použití |

Snadnější použití s programováním prostřednictvím E2Prom nebo FastFlash.

Není vyžadován žádný externí paměťový čip |

Vyžaduje externí paměť pro ukládání programování

informace, které vedou ke složitějšímu použití |

|

Rychlost a předvídatelnost |

Rychlejší rychlost a lepší předvídatelnost načasování kvůli

Střesitelné propojení mezi logickými bloky |

Pomalejší rychlost a méně předvídatelné načasování způsobené

Programování a distribuované propojení na úrovni brány |

|

Technologie programování |

Používá programování E2Prom nebo Flash Memory.Programovací data

je zachován, když je systém vypnut.Podporuje programování na a

programátor nebo systém |

Na základě programování SRAM.Data programování se ztratí, když

Systém je vypnutý a musí být znovu načten.Podporuje dynamiku

konfigurace |

|

Důvěrnost |

Nabízí lepší důvěrnost |

Poskytuje nižší důvěrnost |

|

Spotřeba energie |

Obecně vyšší spotřeba energie, zejména s

vyšší integrace |

Nižší spotřeba energie ve srovnání s CPLD |

Programovací jazyky CPLD

Analýza toho, jak jsou naprogramována složitá programovatelná logická zařízení (CPLD), je základním kamenem při vytváření všestranných hardwarových řešení.Historické metody pro programování CPLD se spoléhaly na žebříkové diagramy nebo hardwarové popis jazyky (HDL), přičemž převládající volbou Verilog HDL a VHDL.Vybraný jazyk může utvářet konstrukční strategii i provozní efektivitu implementací.

• • Verilog Hdl: Verilog HDL je vážena pro svou jednoduchou syntaxi a robustní simulační schopnosti, což odráží metodiky používané v designu digitální logiky.Jeho integrace s nástroji Electronic Design Automation (EDA) vám umožňuje hladce provádět syntézu a simulaci.Bylo pozorováno, že Syntaxe podobné C verilog snižuje bariéru pro vstup pro osoby s programovacím pozadím, čímž urychluje cestu od designu k nasazení napříč širokou škálou průmyslových odvětví.

• • VHDL: VHDL poskytuje propracovanější a výraznější možnost pro programování HDL.Je to často volba pro projekty, které vyžadují pečlivou dokumentaci a přísnou kontrolu typu, rysy oceněné v leteckém a obranném průmyslu.Můžete si uvědomit, že navzdory potenciální složitosti VHDL v menších projektech její disciplinovaná struktura podporuje vytváření výjimečně spolehlivých návrhů, což je nutnost v prostředích, kde je bezpečnost dominantní.

O nás

ALLELCO LIMITED

Přečtěte si více

Rychlý dotaz

Zašlete prosím dotaz, budeme odpovědět okamžitě.

Tranzistory NMOS: design, provoz a aplikace

na 2024/12/29

Rychlá Fourierova transformace (FFT): revoluce zpracování digitálního signálu

na 2024/12/29

Populární příspěvky

-

Komplexní instrukční sada Počítače: Jak změnily výpočetní techniku?

na 8000/04/18 147765

-

USB-C pinout a funkce

na 2000/04/18 111990

-

Použití primitiv simulace Xilinx Unified: Komplexní průvodce designem a simulací FPGA

na 1600/04/18 111351

-

Napájecí napětí v elektronice: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/18 83751

-

Průvodce konektorem RJ45: Pinout, zapojení, typy kabelů a použití

na 1970/01/1 79547

-

Konečný průvodce barevnými kódy drátu v moderních elektrických systémech

Způsob, jakým naše elektrické systémy používají barvy, není jen pro vzhled.Každá barva drátu nyní označuje specifickou funkci, což usnadňuje správnou identifikaci a zpracování elektrických komponen...na 1970/01/1 66949

-

Průvodce čištění ventilu: funkce, příznaky, testování a náhrada za optimální výkon motoru

Vyčistit ventil je klíčovou součástí systému automobilu, který pomáhá udržovat vzduch čistý správou palivových párů, než mohou uniknout do atmosféry.To nejen pomáhá životnímu prostředí snížením zne...na 1970/01/1 63094

-

Kvalita (Q) Faktor: Rovnice a aplikace

Faktor kvality, neboli „Q“, je důležitý při kontrole toho, jak dobře induktory a rezonátory pracují v elektronických systémech, které používají rádiové frekvence (RF).„Q“ měří, jak dobře obvod mini...na 1970/01/1 63028

-

Dosažení maximálního výkonu s maximální větou přenosu energie

Maximální věta o přenosu výkonu vysvětluje, jak energie ze zdroje, jako je baterie nebo generátor, proudí do připojeného zatížení.Ukazuje přesnou podmínku, kdy zatížení přijímá nejvíce energie.Tent...na 1970/01/1 54092

-

Specifikace a kompatibilita baterie A23

Baterie A23 je malá baterie ve tvaru válce s vysokým napětím.Také se nazývá 23A, 23AE nebo MN21, běží při 12 voltech a mnohem vyšší než AA nebo AAA baterie.Díky jeho speciálnímu designu je...na 1970/01/1 52174